# **USER MANUAL**

**ProDAQ VXI Data Acquisition Systems**

# ProDAQ 3180 Ultra-performance Motherboard

PUBLICATION NUMBER: 3180-XX-UM-0100

Copyright, © 2014, Bustec Production, Ltd.

Bustec Production, Ltd. Bustec House, Shannon Business Park, Shannon, Co. Clare, Ireland Tel: +353 (0) 61 707100, FAX: +353 (0) 61 707106

## **PROPRIETARY NOTICE**

This document and the technical data herein disclosed, are proprietary to Bustec Production Ltd., and shall not, without express written permission of Bustec Production Ltd, be used, in whole or in part to solicit quotations from a competitive source or used for manufacture by anyone other than Bustec Production Ltd. The information herein has been developed at private expense, and may only be used for operation and maintenance reference purposes or for purposes of engineering evaluation and incorporation into technical specifications and other documents, which specify procurement of products from Bustec Production Ltd. This document is subject to change without further notification. Bustec Production Ltd. Reserve the right to change both the hardware and software described herein.

## TABLE OF CONTENTS

| CHAPTER 1 - INTRODUCTION                          | 5  |

|---------------------------------------------------|----|

| 1.1 Overview                                      | 5  |

| CHAPTER 2 - GETTING STARTED                       | 7  |

| 2.1 Unpacking and Inspection                      | 7  |

| 2.2 Installing the ProDAQ 3180 Motherboard Module |    |

| 2.2.1 Logical Address Configuration               |    |

| 2.2.2 Installing the ProDAQ 3180 Module           |    |

| 2.2.3 Installing the VXIplug&play Driver          |    |

| CHAPTER 3 - THEORY OF OPERATION                   | 13 |

| 3.1 Overview                                      |    |

| 3.1.1 The VXIbus Interface                        |    |

| 3.1.2 The Memory Controller                       |    |

| 3.1.3 The Function Card Controller                |    |

| 3.2 Modes of Operation                            |    |

| 3.2.1 Direct Function Card Access                 |    |

| 3.2.2 DSP-Supported Function Card Access          |    |

| 3.2.3 Custom DSP Applications                     |    |

| CHAPTER 4 - PROGRAMMING DETAILS                   | 17 |

| 4.1 VXIbus Interface                              |    |

| 4.2 VXIbus Configuration Register                 |    |

| 4.2.1 VXIbus Configuration Register Map           |    |

| 4.2.2 VXIbus Configuration Register Details       |    |

| 4.3 VXIbus A32 Address Range                      |    |

| 4.3.1 VXIbus A32 Address Range Map                |    |

| 4.3.2 Common Registers                            |    |

| 4.3.3 Common Register Details                     |    |

## **Table of Figures**

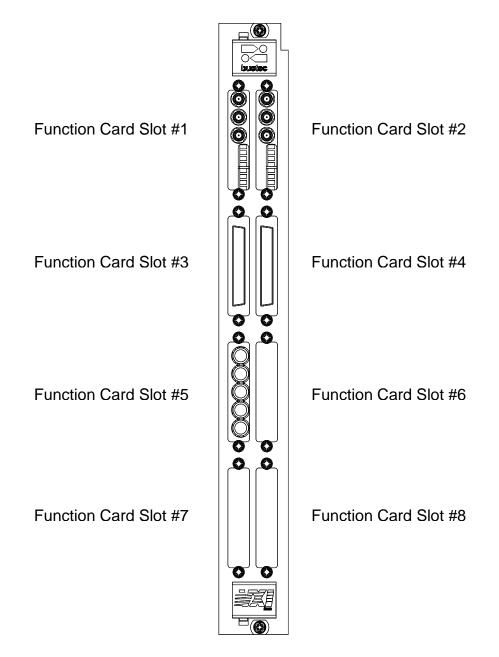

| Figure 1 - ProDAQ 3180 Module Labels<br>Figure 2 - ProDAQ 3180 Function Card Slot Numbering |                                |

|---------------------------------------------------------------------------------------------|--------------------------------|

| Figure 3 - Logical Address Switch                                                           |                                |

| Figure 4 - Installing the ProDAQ 3180 into a C-Size Mainfra                                 |                                |

| Figure 5 - Selecting the Type of Installation                                               | Error! Bookmark not defined.   |

| Figure 6 - Selecting Components for Installation.                                           |                                |

| Figure 7 - Selecting Installation Options                                                   | Error! Bookmark not defined.   |

| Figure 8 - Finishing the Setup                                                              | . Error! Bookmark not defined. |

## Chapter 1 - Introduction

## 1.1 Overview

The 3180 Ultra-performance Motherboard is a single-slot, C-size VXIbus register-based device able to accommodate up to eight ProDAQ function cards. Like its predecessors, the ProDAQ 3120 and ProDAQ 3150 motherboards, it offers not only direct access to the function cards, but also common resources like additional power supplies and trigger routing.

Through its modular design it offers not only to mix and match the functionalities of the ProDAQ function cards to handle a data acquisition or control task, but it also allows for further enhancements by installing the following options:

- The ProDAQ 3280 TigerSHARC DSP Plug-in can be installed in a ProDAQ 3180 motherboard offering standard and custom real-time data processing and handling. It utilizes a TigerSHARC DSP with a clock speed of 400 MHz, providing unmatched 4800 MMACs of 16-bit performance and 3600 MFLOPS of floating-point performance. The firmware and customer programs can be stored in the 16 MByte on-board FLASH. For program execution the DSP offers 24 Mbit on-chip embedded DRAM internally organized in six banks with user-defined partitioning. The 14 channel, zero overhead DMA controller can be used to move data between the on-chip memory and the function cards or the SDRAM memory module on the ProDAQ 3180 motherboard.

- The ProDAQ 3214 DDR2 SDRAM module can be installed in a ProDAQ 3180 motherboard offering up to 1 GByte of high-speed memory for local data storage, data processing and buffering.

- The ProDAQ 3202 Voltage Reference Plug-in can be installed in a ProDAQ 3180 motherboard offering the possibility to internally calibrate ProDAQ function cards installed on the motherboard on-the-fly, without disconnecting from the device under test. It directly provides highly stable, low noise, temperature compensated reference voltages to the function cards, where multiplexers in the analog front-ends can be used to switch them into the input path.

The main improvements in comparison to the existing ProDAQ motherboards 3120 and 3150 are support for the 2eVME protocol as defined by the VXIbus Specification Rev.3; an improved function card interface, which allows for up to 4-times the speed by being backwards compatible; improved data transfer speed to/from the DSP processor and an improved memory module interface now able to accommodate up to 1 GByte DDR2 PC800 SDRAM.

## **Chapter 2 - Getting Started**

The ProDAQ 3180 module is a single slot, C-size VXIbus instrument and can be installed in any slot of a standard C-size VXI mainframe except for the leftmost slot (slot "0"). It will be shipped with all ordered options and function cards pre-installed and its logical address set for dynamic configuration, so that it can be directly installed into the VXIbus system without the need for any additional configuration.

## 2.1 Unpacking and Inspection

All ProDAQ modules are shipped in an antistatic package to prevent any damage from electrostatic discharge (ESD). Proper ESD handling procedures must always be used when packing, unpacking or installing any ProDAQ module, ProDAQ plug-in module or ProDAQ function card:

- Ground yourself via a grounding strap or similar, e.g. by holding to a grounded object.

- Remove the ProDAQ module from its carton, preserving the factory packaging as much as possible.

- Discharge the package by touching it to a grounded object, e.g. a metal part of your VXIbus chassis, before removing the module from the package.

- Inspect the ProDAQ module for any defect or damage. Immediately notify the carrier if any damage is apparent.

- Only remove the module from its antistatic bag if you intend to install it into a VXI mainframe or similar.

When reshipping the module, use the original packing material whenever possible. The original shipping carton and the instrument's plastic foam will provide the necessary support for safe reshipment. If the original anti-static packing material is unavailable, wrap the ProDAQ module in anti-static plastic sheeting and use plastic spray foam to surround and protect the instrument.

The configuration of the module can be verified by examining the two labels on the cover of the module. The first label shows the specifications of the motherboard itself, including the installed options; while the second label shows the configuration of the installed function cards.

Figure 1 shows an example of a set of module labels for the ProDAQ 3180 motherboard with a serial number of 512872, which has the optional ProDAQ 3280 TigerSHARC DSP plug-in with a serial number of 176223 and the ProDAQ 3214 DDR2 SDRAM module with a serial number of 32140012 installed. Two function cards ProDAQ 3424-AA are installed in slots 1-3 and 2-4 (the ProDAQ 3424 is a double-wide function card) and a ProDAQ 3550 is installed in slot 5.

| Serial No. | 512872                        | Note:<br>Specification for           | Voltage | Current |

|------------|-------------------------------|--------------------------------------|---------|---------|

| Power:     | 7.4 W                         | basic configuration                  | +24V    | 10 mA   |

| Cooling:   | 2 1/s @ 0.25 mm H2O           | only. The actual                     | +12V    | 0 mA    |

| Temp.:     | 0°C - 50°C                    | ourrent consumption<br>may depend on | +5V     | 1330 mA |

| Weight:    | 1400 gr.                      | options and function                 | -27     | 25 mA   |

| Options:   | 3280-AA S/N 176223            | cards fitted is the module.          | -5.2V   | 30 mA   |

|            | 3214-AA S/N 32140012          | 10.92643                             | -12V    | 0 mA    |

|            | 140.00.0279/4310/234226.02=-1 | Made in the E.C.                     | -24V    | 10 mA   |

|        |         | 1       |   | _    | n Card  |        |      |     |

|--------|---------|---------|---|------|---------|--------|------|-----|

| Slot   | 1       | 2       | 3 | 4    | 5       | 6      | 7    | 8   |

| Type   | 3424-AA | 3424-AA |   | - 28 | 3550-BC | - 86.1 | 1000 | 1.1 |

| S/N    | 287533  | 287526  |   |      | 543092  |        |      |     |

| Power  | 18.4W   | 18.4W   |   |      | 3.2W    |        |      |     |

| Temp.  | 0*-50°C | 0°-50°C |   |      | 0*-50*C |        |      |     |

| Weight | 195gr.  | 195gr.  |   |      | 100gr.  |        |      |     |

| +24V   | 220     | 220     |   |      | 32      |        |      |     |

| +12V   | 50      | 59      |   |      | 53      |        |      |     |

| +5V    | 1000    | 1000    |   |      | 267     |        |      |     |

| -2V    | 80      | 80      |   |      | 0       |        |      |     |

| -5.2V  | 470     | 470     |   |      | 0       |        |      |     |

| -12V   | 50      | 50      |   |      | 54      |        |      |     |

| -24V   | 180     | 180     |   |      | 23      |        |      |     |

Figure 1 - ProDAQ 3180 Module Labels

## 2.2 Installing the ProDAQ 3180 Motherboard Module

The ProDAQ 3150 Motherboard is fully software configurable. No strap or switch settings are necessary except for the VXI Logical Address setting as specified by the VXIbus standard.

## 2.2.1 Logical Address Configuration

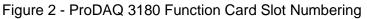

Each device in a VXIbus system is assigned a logical address, either statically by the user or dynamically by the resource manager. This logical address, a number between 0 and 255, defines the base address of the board's VXIbus configuration registers in A16 space. Logical address 0 is reserved for the resource manager, and address 255 is used to tell the resource manager to configure the board's logical address dynamically. In this case the resource manager assigns a free logical address to the board.

The logical address of the board can be set by changing the setting of the 8-bit DIP switch on the back of the board (See Figure 3). The "Open" or "Off" position of a switch corresponds to a logic value of 1 and the "Closed" or "On" position to a logic value of 0. Keep in mind that each board in the system must be assigned its own unique logical address (if configured statically) when setting the switch.

Figure 3 - Logical Address Switch

The ProDAQ 3180 module is shipped with the logical address set to 255. If a static logical address shall be assigned to the module, change the setting of the DIP switch before installing the module into the VXIbus mainframe.

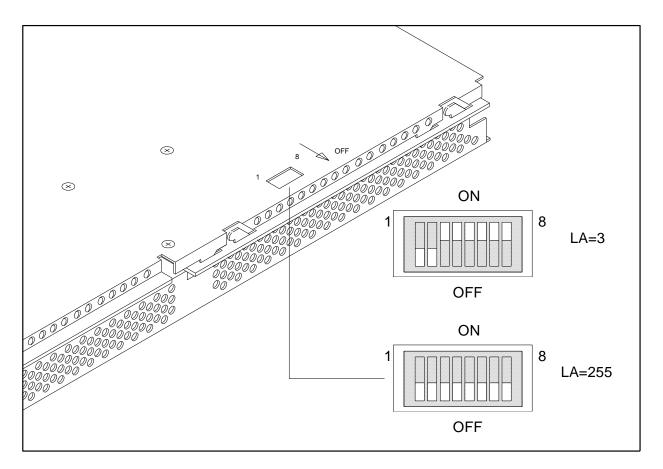

## 2.2.2 Installing the ProDAQ 3180 Module

To prevent damage to the ProDAQ module being installed, it is recommended to remove the power from the mainframe or to switch it off before installing.

Insert the module into the mainframe using the guiding rails inside the mainframe as shown in Figure 4. Push the module slowly into the slot until the modules backplane connectors seat firmly in the corresponding backplane connectors. The top and bottom of the front panel of the module should touch the mounting rails in the mainframe.

Figure 4 - Installing the ProDAQ 3180 into a C-Size Mainframe

## Important:

To ensure proper grounding of the module, tighten the front panel mounting screws after installing the module in the mainframe.

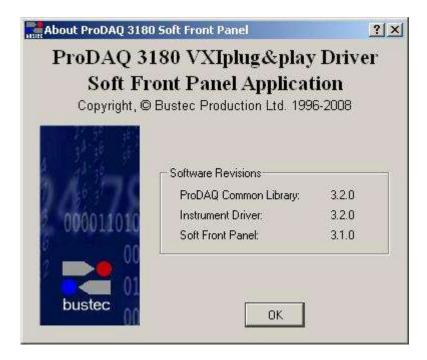

## 2.2.3 Installing the VXI*plug&play* Driver

The ProDAQ 3180 Motherboard is supplied with a VXI*plug&play* driver for the WIN32 framework, Linux and VxWorks<sup>®</sup>. The driver is marked with a version number of the format

<major release>.<minor release>.<patch level>

As the function card drivers rely on the motherboard driver for the communication with the function cards, they share common structures and an internal API with the motherboard driver.

## NOTE:

For the function card and motherboard drivers to work together, all installed drivers must be of the same major and minor version. The patch level may differ.

## NOTE:

## It is recommended to install the VISA library prior to installing any motherboard or function card driver.

#### 2.2.3.1 WIN32 Framework Installation

On the distribution CD, the driver is located in the subdirectory "\Driver\ProDAQ 3180\WIN32". If you have downloaded the driver from the WEB, it is contained in a ZIP archive. Please unpack the ZIP archive into a temporary subdirectory of your choice before starting the installation.

To install the driver, run the "Setup.exe" application coming with it and follow the instructions presented. Make sure that no other ProDAQ software is running when you start the setup.

The installation program by default performs a complete installation. It installs the driver files in the directory tree defined by the %VXIPNPPATH% environment variable and the shortcuts into the VXIPNP program group of the start menu. To choose a different path and/or custom installation options is not recommended and may result in malfunctioning of the soft front panel and any application trying to use the driver.

#### 2.2.3.2 Linux Installation

On the distribution CD, the driver is located in the subdirectory "\Driver\ProDAQ 3180\Linux". It is contained in an RPM archive, which can be directly used for the installation.

To install the driver, run "rpm -i bu3180-x.x.rpm". On most systems, you will need to have superuser rights or use the "sudo" command for a successful installation.

The installation program by default performs a complete installation. It installs the driver files in the directory tree defined by the %VXIPNPPATH% environment variable. To

choose a different path and/or custom installation options is not recommended and may result in malfunctioning of the soft front panel and any application trying to use the driver.

## NOTE:

The installation described here only applies to desktop Linux installations. For embedded systems using a cross-development environment the installation may differ. Refer to the cross-development environments documentation for more information.

#### 2.2.3.3 VxWorks Installation

On the distribution CD, the driver is located in the subdirectory "\Driver\ProDAQ 3180\VxWorks". It is contained in a ZIP archive. In addition to the version number of the driver, the archive name also shows the version of the VxWorks operating system it is precompiled for ("vx<major>.<minor>") and the architecture it is compiled for:

bu3180-<major>.<minor>.<patch>-vx<major>.<minor>-<arch>.zip

where <arch> can be for example "<pentium>" Of "<ppc>".

The archive contains files with paths relative to the root of the standard VXI*plug&play* directory tree. It is recommended to install all drivers into the same subdirectory tree.

## **Chapter 3 - Theory of Operation**

The ProDAQ 3180 Ultra-performance Motherboard is a single-slot C-size VXIbus module able to accommodate up to eight ProDAQ function cards, a DSP plug-in, a memory module and a voltage reference plug-in. It provides the common resources necessary for these components to be part of a VXIbus system, like for example a VXIbus interface, common registers and trigger routing.

## 3.1 Overview

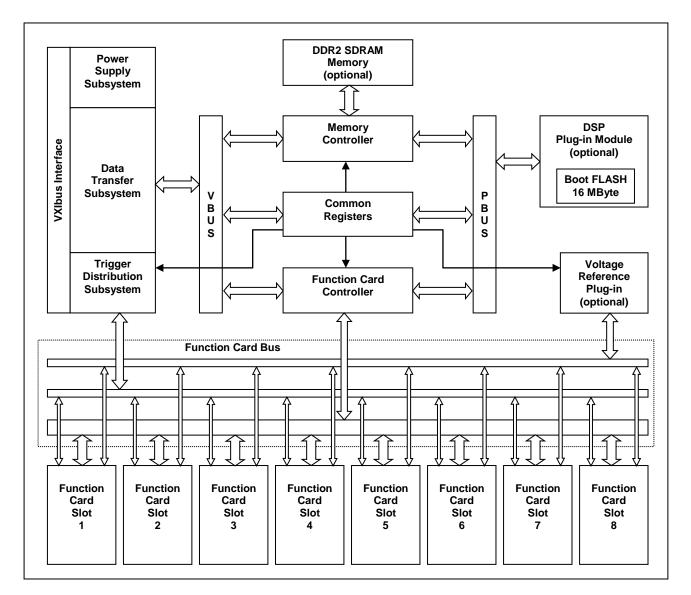

The ProDAQ 3180 Motherboard features a multi-bus architecture to optimize the data flow between the VXIbus interface, the ProDAQ function cards, the memory and the DSP. Figure 5 shows a simplified block diagram of the ProDAQ 3180.

Figure 5 - ProDAQ 3180 Block Diagram

Two high-speed, 32-bit wide internal busses are used to transfer the data between the different parts of the system. The VBus (VXI-side bus) allows masters on the VXIbus (via the VXIbus interface) read/write access to the board resources like memory, function cards and internal registers via the VXIbus interface. It uses a synchronous pipelined protocol and has a maximum throughput rate of 160 MByte/s. The PBus (Processor-side bus) does the same for the optional TigerSHARC DSP. To improve the real-time data processing, it runs at twice the clock frequency of the VBus, allowing for a maximum data throughput of 320 MByte/s.

The memory controller acts as a bus bridge between the VBus/PBus and the standard DDR2 SDRAM bus. The SDRAM bus can interface single bank memory modules with a sustained data rate of more then 512 MByte/s. A read/write cache and a special shadow mode, where data transferred over the PBus to the DSP is shadowed (simultaneously copied) into a memory bank further improve the overall data throughput.

The up to eight ProDAQ function cards are interfaced to the VBus and PBus via the function card controller. The function card controller contains two independent bus bridges, one for accesses from the VBus to the function cards and one for accesses from the PBus to the function cards to allow simultaneous accesses from both sides to different function cards. The bus bridges also allow access to more then one function card at the same time and implement both the standard bus protocol of the existing ProDAQ function cards plus an enhanced new protocol, pushing the data throughput to a maximum of 320 MByte/s.

## 3.1.1 The VXIbus Interface

The VXIbus interface consists of three subsystems: the power supply subsystem, which is responsible to provide clean power to all parts of the system; the data transfer subsystem, which contains the VXIbus slave and VBus master and forwards all accesses made to the board by a VXIbus master to the internal VBus; and the trigger distribution subsystem, which allows to distribute trigger signals between the VXIbus trigger lines, the function card trigger lines and the DSP plug-in module.

The data transfer subsystem forwards all accesses to the two address ranges used by the ProDAQ 3180 in the VXIbus A16 and A32 address space onto the internal VBUS. The VXIbus A16 address range allows access to the configuration registers and can be accessed using D08(EO)/D16/D32 transactions. The A32 range allows access to the function cards, the memory and common registers. It supports D16/D32, D16/D32 BLT, MBLT and 2eVME transactions. To better coordinate the internal data transfer, the data transfer subsystem utilizes both posted writes and prefetching when accessing the different internal resources.

## NOTE:

In order to use MBLT or 2eVME transactions, the slot-0 controller/VXIbus master used MUST be able to generate such cycles. Please refer to your slot-0 controller hardware documentation. In addition the hardware access library/driver used (e.g. the VISA library) must be able to select such a mode.

The trigger distribution subsystem allows to route trigger signals between the VXIbus TTL and ECL trigger lines and the function card trigger in/out lines. The trigger events can also be used to generate a VXIbus interrupt.

## 3.1.2 The Memory Controller

The memory controller contains two local bus slaves, one monitoring the transactions on the VBus, while the other one monitors the transaction on the PBus. The high data bandwidth of the DDR2 SDRAM together with an internal arbiter allow for nearly simultaneous accesses to the memory from both busses. A cache controller implements a write-through cache to further speed up the accesses and translate them into the necessary burst read/writes for the SDRAM.

Due to the limited size of the ProDAQ 3180s VXIbus A32 address range (256 MByte), the local bus slave for the VBus maps three windows of 64 MBytes size from the SDRAM memory space into the VBus space. The start address of each window is programmable.

The local bus slave for the PBus features a special "shadow" mode, where either read accesses generated by the DSP in the function card address space are simultaneously copied to the memory or read accesses generated by the DSP for the memory are simultaneously copied to the function cards. This provides raw data streamed to/from the function cards to an application program running on the DSP for further processing without duplicating read/write accesses.

## 3.1.3 The Function Card Controller

The function card controller implements two complete local bus slaves/function card interfaces, one for accesses from the VBus and one for accesses from the PBus. An arbiter coordinates the accesses, allowing simultaneous accesses to different function cards from the VBus and PBus. Scheduling only occurs if the same function card is accessed simultaneously from both sides.

Both local bus slaves/function card interfaces implement windows for accesses to single function cards, windows for simultaneous accesses to two or four function cards and a special window for broadcast writes to all function cards.

## 3.2 Modes of Operation

The ProDAQ 3180 Motherboard implements the complete functionality to operate ProDAQ function cards in a VXIbus system. The application software and function card drivers can directly access the function card registers to control the cards functions and read/write the data. However, to reach the maximum performance, the optional DSP plug-in module and the DDR2 SDRAM memory are utilized to scatter/gather the data to/from the function cards and allow for an optimized data transfer via the VXIbus.

## 3.2.1 Direct Function Card Access

When the ProDAQ 3180 Motherboard is used without the ProDAQ 3280 TigerSHARC DSP Plug-in and the ProDAQ 3214 DDR2 SDRAM option, either because the options are not installed, the TigerSHARC DSP is used to execute a custom application or just by choice, the ProDAQ 3180 Motherboard allows direct access to the function cards via its A32 address range for the function card drivers. The ProDAQ VXI*plug&play* drivers automatically detect the availability of the DSP plug-in and memory and switch to direct access if they are not available.

## 3.2.2 DSP-Supported Function Card Access

If the ProDAQ 3280 TigerSHARC DSP Plug-in and the ProDAQ 3214 DDR2 SDRAM option are installed and available, the ProDAQ function card drivers use the DSP to execute part of their functionality. These so-called lists can support and speed up common tasks as for example initialization and set-up as well as data acquisition and generation. For the later, each function card gets assigned a buffer in the DDR2 SDRAM, which is used by the driver to de-couple and speed up the data transfer to and from the function card.

## NOTE:

The DSP utilization by the ProDAQ VXI*plug&play* drivers varies from function card to function card depending on its functionality. Please refer to the function card driver documentation for more information.

#### 3.2.3 Custom DSP Applications

ohdoh

## **Chapter 4 - Programming Details**

## 4.1 VXIbus Interface

The VXIbus interface conforms to the VXI-1 Rev. 3.0 Specification and supports access to the boards configuration registers located in the VXIbus A16 address space and the additional image located in the VXIbus A32 address space. The base address of the configuration registers in the A16 address space can be calculated by:

A16 Base Address = 49152 + Logical Address \* 64

The logical address is determined either statically by configuring the board for a logical address in the range of 1 to 254 or by the resource manager when configuring the board for dynamic configuration by using a logical address of 255 (see 2.2.1 : Logical Address Configuration). The configuration registers can be accessed using D08(EO)/D16/D32 transactions.

The resource manager always assigns the base address of the board's address range in the VXIbus A32 address space dynamically. The A32 range allows access to the function cards, the memory and common registers. It supports D16/D32, D16/D32 BLT, MBLT and 2eVME transactions.

## 4.2 VXIbus Configuration Register

## 4.2.1 VXIbus Configuration Register Map

The following table shows a map of the VXIbus configuration registers. The offset shown is relative to the A16 base address.

| Offset    | Name                            | Access | Description                            |

|-----------|---------------------------------|--------|----------------------------------------|

| 0.400     | ID                              | RO     | ID Register                            |

| 0x00      | LA                              | WO     | Logical Address Register               |

| 0x02      | DeviceType                      | RO     | Device Type Register                   |

| 0x04      | Status                          | RO     | Status Register                        |

| 0x06      | Control                         | WO     | Control Register                       |

| 0,00      | Offset                          | RW     | Offset Register                        |

| 0x08-0x10 | 0x08-0x10 <reserved></reserved> |        | -                                      |

| 0x12      | 0x12 Interrupt                  |        | Interrupt Control and Status Register  |

| 0x14      | 0x14 FC Prefetch Size           |        | Function Card Prefetch Size Register   |

| 0x16      | 0x16 MI Prefetch Size           |        | Memory Images Prefetch Size Register   |

| 0x18      | FC Write Threshold              | RW     | Function Card Write Threshold Register |

| 0x1A      | MI Write Threshold              | RW     | Memory Images Write Threshold Register |

| 0x1C      | <reserved></reserved>           | -      | -                                      |

| 0x1E      | Word Swap                       | RW     | Word Swap Control Register             |

| 0x20-0x30 | <reserved></reserved>           | -      | -                                      |

| 0x32      | Option Type                     | RO     | Option Type Identification Register    |

| 0x34-0x3E | <reserved></reserved>           | -      | -                                      |

Table 1 - VXIbus Configuration Register

## 4.2.2 VXIbus Configuration Register Details

## 4.2.2.1 ID Register

| Bit   | Access<br>Default | Description                                                                                                                                                                             |

|-------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | RO                | Device Class                                                                                                                                                                            |

| 15:14 | 0x3               | This field defines the module as a register based VXIbus device                                                                                                                         |

|       | RO                | Address Space                                                                                                                                                                           |

| 13:12 | 0x1               | This field determines the address ranges used by the device. The ProDAQ 3180 uses a range in the A32 address space in addition to the configuration registers in the A16 address range. |

|       | RO                | Manufacturer ID                                                                                                                                                                         |

| 11:0  | 0xE70             | The Manufacturer ID is 0xE70 and has been assigned by the VXIbus Consortium. This number uniquely identifies the manufacturer of the device as "Bustec Production Ltd."                 |

## 4.2.2.2 Logical Address Register

| Bit  | Access<br>Default | Description                                                                                                                                                                                                                                                                                |

|------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8 | -                 | Reserved                                                                                                                                                                                                                                                                                   |

| 7:0  | wo                | Logical Address<br>Used by the resource manager to assign a logical address to the module during the<br>dynamic configuration phase. These bits are updated only if DC configuration has<br>been selected (LA switch set to 255) and MODID line has been asserted for the given<br>module. |

## 4.2.2.3 Device Type Register

| Bit   | Access<br>Default | Description                                                                                                                    |

|-------|-------------------|--------------------------------------------------------------------------------------------------------------------------------|

|       | RO                | Required Memory                                                                                                                |

| 15:12 | 0x3               | This field defines the window size required by the board in A32 address space. The value of 0x3 indicates a size of the 256MB. |

| 11:0  | RO                | Model Code                                                                                                                     |

| 11.0  | 0xC6C             | This field contains a unique device identifier: 0xC6C => 3180                                                                  |

## 4.2.2.4 Status Register

| Bit   | Access<br>Default | Description                                                                                                                                                                                                                                                  |

|-------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | RO                | A32 Active                                                                                                                                                                                                                                                   |

| -     | 0                 | This bit reflects the state of the Control register's A32 Enable bit.                                                                                                                                                                                        |

|       | RO                | MODID*                                                                                                                                                                                                                                                       |

| 14    | н                 | A one (1) indicates that the device is not selected via the P2 MODID line. A zero (0) indicates that the device is selected by a high state on the MODID line.                                                                                               |

| 13    | RO                | SGLWR_POSTED – Single Write Posted                                                                                                                                                                                                                           |

|       | 0                 | A one (1) indicates the next A32 single write as posted.                                                                                                                                                                                                     |

| 12:10 | -                 | Reserved                                                                                                                                                                                                                                                     |

|       | RO                | ITIMEOUT_CLEANUP – Internal Timeout Cleanup                                                                                                                                                                                                                  |

| 9     | н                 | When set this bit indicates that the cleanup after internal timeout is in course and the board is not accessible in A32 space                                                                                                                                |

| 0     | ROC               | ITIMEOUT_HAPPENED – Internal Timeout Happened                                                                                                                                                                                                                |

| 8     | н                 | When set this bit indicates that the internal timeout happened. The bit is cleared after readout                                                                                                                                                             |

| 7     | RO                | DSP_AVAIL – DSP Board available                                                                                                                                                                                                                              |

|       | н                 | When set this bit indicates that the ProDAQ 3280 DSP board is installed.                                                                                                                                                                                     |

| 6     | -                 | Reserved                                                                                                                                                                                                                                                     |

|       | RO                | DSP_RES – DSP Reset                                                                                                                                                                                                                                          |

| 5     | н                 | This bit reflects the state of the DSP_RES bit                                                                                                                                                                                                               |

| 4     | RO                | DSP_RDY – DSP Ready                                                                                                                                                                                                                                          |

| т     | н                 | A one (1) indicates that the DSP finished the booting.                                                                                                                                                                                                       |

| _     | RO                | Ready                                                                                                                                                                                                                                                        |

| 3     | н                 | A zero (0) indicates that the module has not completed its initialization process and is executing its self-test.                                                                                                                                            |

|       | RO                | Passed                                                                                                                                                                                                                                                       |

| 2     | н                 | After the self-test completion (signaled by a one (1) in the Ready bit), the Passed bit indicates the status of the self-test. A one (1) indicates that the self-test has successfully completed. A zero (0) means that the device has failed its self-test. |

| 1     | -                 | Reserved                                                                                                                                                                                                                                                     |

| _     | RO                | SOFT_RESET – Software Reset                                                                                                                                                                                                                                  |

| 0     | 0                 | This bit reflects the state of the SOFT_RESET: if set then the software reset is in course                                                                                                                                                                   |

## 4.2.2.5 Control Register

| Bit  | Access<br>Default | Description                                                                                                                                                                                                                                                                                 |

|------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | WO                | A32 Active                                                                                                                                                                                                                                                                                  |

| 15   | 0                 | Writing a one (1) to the bit enables accesses to the A32 address space. Writing a zero (0) disables accesses to the A32 address space.                                                                                                                                                      |

| 14   | -                 | Reserved                                                                                                                                                                                                                                                                                    |

|      | wo                | SGLWR_POSTED – Single Write Posted                                                                                                                                                                                                                                                          |

| 13   | 1                 | A zero (0) written to this bit defines the single writes as non-posted. It means that VXI bus slave waits with the A32 single write completion until it gets confirmation from FC or Common Registers controller that the word reached the destination.                                     |

| 12:6 | -                 | Reserved                                                                                                                                                                                                                                                                                    |

|      | wo                | DSP_RES – DSP Reset                                                                                                                                                                                                                                                                         |

| 5    | 1                 | A one (1) written to this bit place the DSP in reset. After power up the host has to release the reset to let the DSP start booting. Releasing reset after power on could be done automatically if DSP_STANDALONE_N bit in the EEPROM is set to zero.                                       |

| 4:2  | -                 | Reserved                                                                                                                                                                                                                                                                                    |

|      | WO                | Sysfail Inhibit                                                                                                                                                                                                                                                                             |

| 1    | 0                 | A one (1) written to this bit disables the device from driving the SYSFAIL* line.                                                                                                                                                                                                           |

|      |                   | SOFT_RESET – Software Reset                                                                                                                                                                                                                                                                 |

| 0    | WO<br>0           | Writing a one (1) to the bit reset the module (device goes into reset state). Writing a zero (0) clears the reset.<br>SOFT_RESET clears all state machines and all registers in Common Register address space but A16 Slave and some Configuration Registers are not affected by this reset |

## 4.2.2.6 Offset Register

| Bit   | Access<br>Default | Description                                                                                                                         |

|-------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|

|       | RW                | Offset                                                                                                                              |

| 15:12 | 0                 | The bits define the base address of the device in the VXI A32 address space. The bits 15:12 are mapped to the address lines A31:A28 |

### 4.2.2.7 Interrupt Register

| Bit  | Access<br>Default | Description                                                                                                                                                                                     |

|------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | RO                | IRQ_STS[7:1] – IRQ Status                                                                                                                                                                       |

| 15:9 | н                 | Shows the status of the VXI IRQ lines. A value of '1' means the interrupt line is asserted.                                                                                                     |

| 8:6  | wo                | IRQ_CLR[2:0] – IRQ Clear                                                                                                                                                                        |

| 0.0  | 000               | Writing '101' to these bits clears the IRQ output of the interrupter.                                                                                                                           |

|      | RWC               | SW_INT – Software Interrupt                                                                                                                                                                     |

| 5    | 0                 | The bit is used to generate the interrupt to the VXI bus. When the bit is set the interrupt is generated to the selected IRQ line, The bit is cleared by hardware at the end of the IACK cycle. |

|      | RW                | MBOX_INT_EN – Mailbox Interrupt Enable                                                                                                                                                          |

| 4    | 0                 | The bit is used to enable/disable the mailbox as a source of the interrupt to the VXI bus. When the bit is set this source of the interrupt is enabled.                                         |

|      | RW                | TNODE_INT_EN – Trigger Node Interrupt Enable                                                                                                                                                    |

| 3    | 0                 | The bit is used to enable/disable Trigger Node 20 as a source of the interrupt to the VXI bus. When the bit is set this source of the interrupt is enabled.                                     |

|      |                   | IRQ_LEVEL[2:0] – IRQ Level                                                                                                                                                                      |

|      |                   | The bits select the VXI IRQ line of the interrupter.<br>The values are coded in the following way:                                                                                              |

|      | RW                | 000 : Interrupts disabled                                                                                                                                                                       |

| 2:0  | 0                 | 001 : IRQ1 selected<br>010 : IRQ2 selected                                                                                                                                                      |

|      | Ũ                 | 011 : IRQ3 selected                                                                                                                                                                             |

|      |                   | 100 : IRQ4 selected                                                                                                                                                                             |

|      |                   | 101 : IRQ5 selected<br>110 : IRQ6 selected                                                                                                                                                      |

|      |                   | 111 : IRQ7 selected                                                                                                                                                                             |

## 4.2.2.8 FC Prefetch Size Register

| Bit   | Access<br>Default | Description                     |  |  |

|-------|-------------------|---------------------------------|--|--|

| 15:14 | RW<br>0           | PFS_FC8 – Prefetch Size for FC8 |  |  |

| 13:12 | RW<br>0           | PFS_FC7 – Prefetch Size for FC7 |  |  |

| 11:10 | RW<br>0           | PFS_FC6 – Prefetch Size fo FC6  |  |  |

| Bit | Access<br>Default | Description                     |  |

|-----|-------------------|---------------------------------|--|

| 9:8 | RW<br>0           | PFS_FC5 – Prefetch Size for FC5 |  |

| 7:6 | RW<br>0           | PFS_FC4 – Prefetch Size for FC4 |  |

| 5:4 | RW<br>0           | PFS_FC3 – Prefetch Size of FC3  |  |

| 3:2 | RW<br>0           | PFS_FC2 – Prefetch Size of FC2  |  |

| 1:0 | RW<br>0           | PFS_FC1 – Prefetch Size of FC1  |  |

Each field defines the amount of the data prefetched when accessing the function card. The values are coded in the following way:

- 00 : 1 beat, no prefetching

- 01 : 8 beats

- 10 : 16 beats

- 11:64 beats

The beat size depends on the VXI cycle width, for example for a D16 access one beat means 2 bytes, for a D32 access four bytes, and for a D64 access eight bytes. For double-wide function cards, the prefetch size needs to be set for both positions they are located in. If one of the available modes is used to access several function cards in parallel, the prefetch size used is determined by the smallest size set for the function cards accessed.

#### 4.2.2.9 MI Prefetch Size Register

| Bit  | Access<br>Default | Description                                |  |

|------|-------------------|--------------------------------------------|--|

| 15:6 | -                 | Reserved                                   |  |

| 5:4  | RW<br>0           | S_MI3 – Prefetch Size for Memory Image 3   |  |

| 3:2  | RW<br>0           | PFS_MI2 – Prefetch Size for Memory Image 2 |  |

| 1:0  | RW<br>0           | PFS_MI2 – Prefetch Size for Memory Image 1 |  |

Each field defines the amount of the data prefetched when accessing one of the memory images in the A32 address range. The values are coded in same way as in the function card prefetch size fields above.

#### 4.2.2.10 FC Write Threshold Register

| Bit   | Access &<br>Default                          | Description                       |  |  |

|-------|----------------------------------------------|-----------------------------------|--|--|

| 15:14 | RW<br>0                                      | WTH_FC8 – Write Threshold for FC8 |  |  |

| 13:12 | RW<br>0                                      | WTH_FC7 – Write Threshold for FC7 |  |  |

| 11:10 | RW<br>0                                      | TH_FC6 – Write Threshold for FC6  |  |  |

| 9:8   | RW<br>0                                      | WTH_FC5 – Write Threshold for FC5 |  |  |

| 7:6   | RW<br>0                                      | WTH_FC4 – Write Threshold for FC4 |  |  |

| 5:4   | RW<br>0                                      | WTH_FC4 – Write Threshold for FC3 |  |  |

| 3:2   | RW<br>0                                      | WTH_FC4 – Write Threshold for FC2 |  |  |

| 1:0   | RW<br>WTH_FC4 – Write Threshold for FC1<br>0 |                                   |  |  |

Each field defines the amount of the data buffered before accessing a function card. The values are coded in the following way:

00 : 1 beat 01 : 8 beats 10 : 16 beats 11 : 64 beats

The beat size depends on the VXI cycle width, for example for a D16 access one beat means 2 bytes, for a D32 access four bytes, and for a D64 access eight bytes. For double-wide function cards, the write threshold size needs to be set for both positions they are located in. If one of the available modes is used to access several function cards in parallel, the write threshold size used is determined by the smallest size set for the function cards accessed.

#### 4.2.2.11 MI Write Threshold register

| Bit  | Access &<br>Default | Description                                 |  |

|------|---------------------|---------------------------------------------|--|

| 15:6 | -                   | Reserved                                    |  |

| 5:4  | RW<br>0             | TH_MI3 – Write Threshold of Memory Image 3  |  |

| 3:2  | RW<br>0             | WTH_MI3 – Write Threshold of Memory Image 2 |  |

| 1:0  | RW<br>0             | WTH_MI3 – Write Threshold of Memory Image 1 |  |

Each field defines the amount of the data buffered before accessing one of the memory images in the A32 address range. The values are coded in same way as in the function card write threshold size fields above.

#### 4.2.2.12 Word Swap Register

This register is used to configure the word swapping used for D32, MBLT and 2eVME accesses. The word swapping logic swaps the upper 16-bit word with the lower 16-bit word for D32 access. For MBLT and 2eVME accesses it swaps the two upper words with each other and the two lower words in the same way. Word swapping works for read and write accesses.

| Bit | Access<br>Default | Description                                                                                                                                                                                                                                    |

|-----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | -                 | Reserved                                                                                                                                                                                                                                       |

|     | RW                | WSWAP_QW4 – Word Swap, QW window of FC5-6-7-8                                                                                                                                                                                                  |

| 14  | 0                 | When this bit is set the 16-bit word swapping happens during D64 accesses to the QW window of the FC5-6-7-8. For the D64 first 16-bit word is swapped with the second word, and third word is swapped with the fourth word of the 64-bit data. |

|     | RW                | WSWAP_QW3 – Word Swap, QW window of FC1-2-3-4                                                                                                                                                                                                  |

| 13  | 0                 | When this bit is set the 16-bit word swapping happens during D64 accesses to the QW window of the FC1-2-3-4. For the D64 first 16-bit word is swapped with the second word, and third word is swapped with the fourth word of the 64-bit data. |

|     | RW                | WSWAP_QW2 – Word Swap, QW window of FC2-4-6-8                                                                                                                                                                                                  |

| 12  | 0                 | When this bit is set the 16-bit word swapping happens during D64 accesses to the QW window of the FC2-4-6-8. For the D64 first 16-bit word is swapped with the second word, and third word is swapped with the fourth word of the 64-bit data. |

|     | DW                | WSWAP_QW1 – Word Swap, QW window of FC1-3-5-7                                                                                                                                                                                                  |

| 11  | RW<br>0           | When this bit is set the 16-bit word swapping happens during D64 accesses to the QW window of the FC1-3-5-7. For the D64 first 16-bit word is swapped with the second word, and third word is swapped with the fourth word of the 64-bit data. |

| Access<br>Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RW                | WSWAP_DW8 – Word Swap, DW window of FC7-8                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0                 | When this bit is set the 16-bit word swapping happens during D32 or D64 accesses to the DW window of the FC7-8. For the D64 first 16-bit word is swapped with the second word, and third word is swapped with the fourth word of the 64-bit data.                                                                                                                                                                                                |

| RW                | WSWAP_DW7 – Word Swap, DW window of FC5-6                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0                 | When this bit is set the 16-bit word swapping happens during D32 or D64 accesses to the DW window of the FC5-6. For the D64 first 16-bit word is swapped with the second word, and third word is swapped with the fourth word of the 64-bit data.                                                                                                                                                                                                |

| RW                | WSWAP_DW6 – Word Swap, DW window of FC3-4                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0                 | When this bit is set the 16-bit word swapping happens during D32 or D64 accesses to the DW window of the FC3-4. For the D64 first 16-bit word is swapped with the second word, and third word is swapped with the fourth word of the 64-bit data.                                                                                                                                                                                                |

| RW                | WSWAP_DW5 – Word Swap, DW window of FC1-2                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0                 | When this bit is set the 16-bit word swapping happens during D32 or D64 accesses to the DW window of the FC1-2. For the D64 first 16-bit word is swapped with the second word, and third word is swapped with the fourth word of the 64-bit data.                                                                                                                                                                                                |

| D\//              | WSWAP_DW4 – Word Swap, DW window of FC6-8                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0                 | When this bit is set the 16-bit word swapping happens during D32 or D64 accesses to the DW window of the FC6-8. For the D64 first 16-bit word is swapped with the second word, and third word is swapped with the fourth word of the 64-bit data.                                                                                                                                                                                                |

| D\//              | WSWAP_DW3 – Word Swap, DW window of FC5-7                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0                 | When this bit is set the 16-bit word swapping happens during D32 or D64 accesses to the DW window of the FC5-7. For the D64 first 16-bit word is swapped with the second word, and third word is swapped with the fourth word of the 64-bit data.                                                                                                                                                                                                |

| D\A/              | WSWAP_DW2 – Word Swap, DW window of FC2-4                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0                 | When this bit is set the 16-bit word swapping happens during D32 or D64 accesses to the DW window of the FC2-4. For the D64 first 16-bit word is swapped with the second word, and third word is swapped with the fourth word of the 64-bit data.                                                                                                                                                                                                |

| RW                | WSWAP_DW1 – Word Swap, DW window of FC1-3                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0                 | When this bit is set the 16-bit word swapping happens during D32 or D64 accesses to the DW window of the FC1-3. For the D64 first 16-bit word is swapped with the second word, and third word is swapped with the fourth word of the 64-bit data.                                                                                                                                                                                                |

| D\\/              | WSWAP_MI3 – Word Swap, Memory Image 3                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0                 | When this bit is set the 16-bit word swapping happens during D32 or D64 accesses to Memory Image 3. For the D64 first 16-bit word is swapped with the second word, and third word is swapped with the fourth word of the 64-bit data.                                                                                                                                                                                                            |

| RW                | WSWAP_MI2 – Word Swap, Memory Image 2                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0                 | When this bit is set the 16-bit word swapping happens during D32 or D64 accesses to Memory Image 2. For the D64 first 16-bit word is swapped with the second word, and third word is swapped with the fourth word of the 64-bit data.                                                                                                                                                                                                            |

|                   | Default           RW           0           RW           0 |

| Bit                | Access & Default | Description                                                                |  |

|--------------------|------------------|----------------------------------------------------------------------------|--|

| 15:8               | -                | Reserved                                                                   |  |

| 7:0 RO OPTION_TYPE |                  | OPTION_TYPE<br>The bits show the option type installed in the motherboard. |  |

## 4.3 VXIbus A32 Address Range

The ProDAQ 3180 utilizes an address range of the size of 256 MBytes in the VXIbus A32 address space. Its base address is assigned by the resource manager by writing the upper four bits of the base address into the offset register (see 4.2.2.6) and by enabling the A32 address decoding by writing to the "A32 Active" bit in the control register (see 4.2.2.5).

The A32 address range offers access to the function card address ranges, the memory windows to access the DDR2 SDRAM memory (if installed) and a set of control registers. It accepts the following bus cycles:

- SCT: D16/D32

- BLT: D16/D32

- MBLT

- 2eVME

Some areas do not support D16 and/or D32 accesses as shown below. Please note that unaligned transfers are not supported.

## 4.3.1 VXIbus A32 Address Range Map

The following table shows a map of the VXIbus A32 address range used by the ProDAQ 3180. The offset shown is relative to the base address set in the offset register.

| Offset Range          | Size [kB] | Description                   | Notes |

|-----------------------|-----------|-------------------------------|-------|

| 0x0000000 - 0x1FFFFFF | 128       | Common Registers              |       |

| 0x2000000 - 0x201FFFF | 128       | Function Card 1, SW window    |       |

| 0x2020000 - 0x203FFFF | 128       | Function Card 2, SW window    |       |

| 0x2040000 - 0x205FFFF | 128       | Function Card 3, SW window    |       |

| 0x2060000 - 0x207FFFF | 128       | Function Card 4, SW window    |       |

| 0x2080000 - 0x209FFFF | 128       | Function Card 5, SW window    |       |

| 0x20A0000 - 0x20BFFFF | 128       | Function Card 6, SW window    |       |

| 0x20C0000 - 0x20DFFFF | 128       | Function Card 7, SW window    |       |

| 0x20E0000 - 0x20FFFFF | 128       | Function Card 8, SW window    |       |

| 0x2100000 - 0x21FFFFF | -         | reserved                      |       |

| 0x2200000 - 0x223FFFF | 256       | Function Cards 1-3, DW window | 1     |

| 0x2240000 - 0x227FFFF | 256       | Function Cards 2-4, DW window | 1     |

| Offset Range          | Size [kB] | Description                       | Notes |

|-----------------------|-----------|-----------------------------------|-------|

| 0x2280000 - 0x22BFFFF | 256       | Function Cards 5-7, DW window     | 1     |

| 0x22C0000 - 0x22FFFFF | 256       | Function Cards 6-8, DW window     | 1     |

| 0x2300000 - 0x233FFFF | 256       | Function Cards 1-2, DW window     | 1     |

| 0x2340000 - 0x237FFFF | 256       | Function Cards 3-4, DW window     | 1     |

| 0x2380000 - 0x23BFFFF | 256       | Function Cards 5-6, DW window     | 1     |

| 0x23C0000 - 0x23FFFFF | 256       | Function Cards 7-8, DW window     | 1     |

| 0x2400000 - 0x247FFFF | 512       | Function Cards 1-3-5-7, QW window | 1,2   |

| 0x2480000 - 0x24FFFFF | 512       | Function Cards 2-4-6-8, QW window | 1,2   |

| 0x2500000 - 0x257FFFF | 512       | Function Cards 1-2-3-4, QW window | 1,2   |

| 0x2580000 - 0x25FFFFF | 512       | Function Cards 5-6-7-8, QW window | 1,2   |

| 0x2600000 - 0x261FFFF | 128       | Function Cards, BW window         | 3     |

| 0x2620000 - 0x3FFFFFF | -         | reserved                          |       |

| 0x4000000 - 0x7FFFFFF | 65536     | DDR Memory Window 1               |       |

| 0x8000000 - 0xBFFFFFF | 65536     | DDR Memory Window 2               |       |

| 0xC000000 - 0xFFFFFFF | 65536     | DDR Memory Window 3               |       |

Notes:

- 1 D16 is not supported for this window

- 2 D32 is not supported for this window

- 3 Only write is allowed

#### 4.3.2 Common Registers

The following table shows a map of the common registers located at the beginning of the A32 address range.

| Offset | Register Name   | Access | Description                                 |

|--------|-----------------|--------|---------------------------------------------|

| 0      | MB_REV          | RO     | Motherboard Revision                        |

| 4      | MB_SN           | RO     | Motherboard Serial Number                   |

| 8      | PB_REV          | RW     | Plug-in Board Revision                      |

| С      | PB_SN           | RO     | Plug-in Board Serial Number                 |

| 10     | VREF_REV        | RO     | Voltage Reference Revision                  |

| 14     | VREF_SN         | RO     | Voltage Reference Serial Number             |

| 18     | I2C_BUS1_CTRL   | RW     | I2C bus #1 control register                 |

| 1C     | I2C_BUS2_CTRL   | RW     | I2C bus #2 control register                 |

| 20     | JTAG_CTRL       | RW     | JTAG chain control register                 |

| 24     | FC_HSDET        | RO     | Function Card High-Speed Detection register |

| 28     | FC_RST          | RW     | Function Card Reset register                |

| 2C     | FC_CTRL_VXI     | RW     | Function Card Control Register for VXI side |

| 30     | FC_CTRL_DSP     | RW     | Function Card Control Register for DSP side |

| 34     | FC_WR_QUEUE_EMP | RO     | Function Card Write Queue Empty             |

| 38     | TN0_CTRL        | RW     | Trigger Node 0 Control Register             |

| Offset | Register Name  | Access | Description                             |

|--------|----------------|--------|-----------------------------------------|

| 3C     | TN1_CTRL       | RW     | Trigger Node 1 Control Register         |

| 40     | TN2_CTRL       | RW     | Trigger Node 2 Control Register         |

| 44     | TN3_CTRL       | RW     | Trigger Node 3 Control Register         |

| 48     | TN4_CTRL       | RW     | Trigger Node 4 Control Register         |

| 4C     | TN5_CTRL       | RW     | Trigger Node 5 Control Register         |

| 50     | TN6_CTRL       | RW     | Trigger Node 6 Control Register         |

| 54     | TN7_CTRL       | RW     | Trigger Node 7 Control Register         |

| 58     | TN8_CTRL       | RW     | Trigger Node 8 Control Register         |

| 5C     | TN9_CTRL       | RW     | Trigger Node 9 Control Register         |

| 60     | TN10_CTRL      | RW     | Trigger Node 10 Control Register        |

| 64     | TN11_CTRL      | RW     | Trigger Node 11 Control Register        |

| 68     | TN12_CTRL      | RW     | Trigger Node 12 Control Register        |

| 6C     | TN13_CTRL      | RW     | Trigger Node 13 Control Register        |

| 70     | TN14_CTRL      | RW     | Trigger Node 14 Control Register        |

| 74     | TN15_CTRL      | RW     | Trigger Node 15 Control Register        |

| 78     | TN16_CTRL      | RW     | Trigger Node 16 Control Register        |

| 7C     | TN17_CTRL      | RW     | Trigger Node 17 Control Register        |

| 80     | TN18_CTRL      | RW     | Trigger Node 18 Control Register        |

| 84     | TN19_CTRL      | RW     | Trigger Node 19 Control Register        |

| 88     | TN20_CTRL      | RW     | Trigger Node 20 Control Register        |

| 8C     | TN21_CTRL      | RW     | Trigger Node 21 Control Register        |

| 90     | TN22_CTRL      | RW     | Trigger Node 22 Control Register        |

| 94     | TN23_CTRL      | RW     | Trigger Node 23 Control Register        |

| 98     | TN24_CTRL      | RW     | Trigger Node 24 Control Register        |

| 9C     | TN25_CTRL      | RW     | Trigger Node 25 Control Register        |

| A0     | TN26_CTRL      | RW     | Trigger Node 26 Control Register        |

| A4     | TN27_CTRL      | RW     | Trigger Node 27 Control Register        |

| A8     | TN28_CTRL      | RW     | Trigger Node 28 Control Register        |

| AC     | TN_SET         | RW     | Trigger Node Set Register               |

| B0     | TN_ENABLE      | RW     | Trigger Node Enable Register            |

| B4     | TN_STATUS      | RO     | Trigger Node Status                     |

| B8     | TN_SRC_STATUS1 | RO     | Trigger Node Source Status Register 1   |

| BC     | TN_SRC_STATUS2 | RO     | Trigger Node Source Status Register 2   |

| C0     | FC_CCLK_SEL    | RW     | FC Common Clock Selection Register      |

| C4     | TM_TEST        | RW     | Trigger Matrix Test Register            |

| C8     | SH0_FC_START   | RW     | Shadow Mode Function Card Start Address |

| CC     | SH0_MEM_START  | RW     | Shadow Mode Memory Start Address        |

| D0     | SH1_FC_START   | RW     | Shadow Mode Function Card Start Address |

| D4     | SH1_MEM_START  | RW     | Shadow Mode Memory Start Address        |

| D8     | SH2_FC_START   | RW     | Shadow Mode Function Card Start Address |

| Offset | Register Name   | Access | Description                             |

|--------|-----------------|--------|-----------------------------------------|

| DC     | SH2_MEM_START   | RW     | Shadow Mode Memory Start Address        |

| E0     | SH3_FC_START    | RW     | Shadow Mode Function Card Start Address |

| E4     | SH3_MEM_START   | RW     | Shadow Mode Memory Start Address        |

| E8     | SH4_MEM_START   | RW     | Shadow Mode Memory Start Address        |

| EC     | SH4_FC_START    | RW     | Shadow Mode Function Card Start Address |

| F0     | SH5_MEM_START   | RW     | Shadow Mode Memory Start Address        |

| F4     | SH5_FC_START    | RW     | Shadow Mode Function Card Start Address |

| F8     | SH6_MEM_START   | RW     | Shadow Mode Memory Start Address        |

| FC     | SH6_FC_START    | RW     | Shadow Mode Function Card Start Address |

| 100    | SH7_MEM_START   | RW     | Shadow Mode Memory Start Address        |

| 104    | SH7_FC_START    | RW     | Shadow Mode Function Card Start Address |

| 108    | SH_CTRL         | RW     | Shadow Mode Control Register            |

| 10C    | DDR_PAGE_IMAGE1 | RW     | DDR Memory Page Image 1 Offset Register |