## **USER MANUAL**

**ProDAQ Data Acquisition Function Cards**

# **ProDAQ 3424 8-Channel, 24-Bit, Sigma-Delta ADC Function Card**

PUBLICATION NUMBER: 3424-XX-UM-0010

Copyright, © 2014, Bustec Production, Ltd.

Bustec Production, Ltd. Bustec House, Shannon Business Park, Shannon, Co. Clare, Ireland Tel: +353 (0) 61 707100, FAX: +353 (0) 61 707106

#### **PROPRIETARY NOTICE**

This document and the technical data herein disclosed, are proprietary to Bustec Production Ltd., and shall not, without express written permission of Bustec Production Ltd, be used, in whole or in part to solicit quotations from a competitive source or used for manufacture by anyone other than Bustec Production Ltd. The information herein has been developed at private expense, and may only be used for operation and maintenance reference purposes or for purposes of engineering evaluation and incorporation into technical specifications and other documents, which specify procurement of products from Bustec Production Ltd.. This document is subject to change without further notification. Bustec Production Ltd. Reserve the right to change both the hardware and software described herein.

## **Table of Contents**

| 1. INTR                                                                                                                                                                                | RODUCTION                                                                                                                                                   | 7            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 2. INST                                                                                                                                                                                | ALLATION                                                                                                                                                    | 8            |

| 2.1.<br>2.2.<br>2.3.<br>2.4.<br>2.5.                                                                                                                                                   | Unpacking and Inspection<br>Reshipment Instructions<br>Preparing the ProDAQ Module<br>Installing a ProDAQ Function Card<br>Removing a ProDAQ Function Card. | 8<br>9<br>10 |

| 3. THE                                                                                                                                                                                 | ORY OF OPERATION                                                                                                                                            | 13           |

| 3.1.<br>3.1.1<br>3.1.2<br>3.1.3<br>3.2.<br>3.2.1<br>3.2.2<br>3.2.3<br>3.3.<br>3.3.1<br>3.3.2<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.6<br>3.3.7<br>3.3.6<br>3.3.6<br>3.3.7<br>3.3.8<br>3.3.9 | <ul> <li>ICP sensor conditioning</li></ul>                                                                                                                  |              |

|                                                                                                                                                                                        |                                                                                                                                                             |              |

| 5. REG<br>5.1.<br>5.2.<br>5.3.<br>5.4.<br>5.5.<br>5.6.<br>5.7.<br>5.8.<br>5.9.<br>5.10.<br>5.11.<br>5.12.<br>5.13.                                                                     | ISTER DESCRIPTION                                                                                                                                           |              |

| 5.14.<br>5.15. | AT_THR_SIGERR – Analog Trigger Threshold / Signal Error Register<br>AT_CTRL – Analog Trigger Control Register |    |

|----------------|---------------------------------------------------------------------------------------------------------------|----|

| 5.16.          | CHNxCFG – Channel x Configuration Register                                                                    |    |

| 5.17.          | DDS_WX – DDS Word Register                                                                                    |    |

| 5.18.          | DAC_DATA – DAC Data Register                                                                                  |    |

| 5.19.          | DAC_ADDR – DAC Address Register                                                                               | 47 |

| 5.20.          | TEDS_ACC – TEDS Access Register                                                                               |    |

| 5.21.          | GCOEFL – Gain correction coefficient write register, bits 150                                                 | 49 |

| 5.22.          | GCOEFH - Gain correction coefficient write register, bits 2316 and address                                    | 49 |

| 5.23.          | EPD – EEPROM Data Register                                                                                    |    |

| 5.24.          | EPC – EEPROM Control Register                                                                                 | 50 |

| 5.25.          | FCSUB – Function Card Sub-Type Register                                                                       | 51 |

| 5.26.          | FCSERH – Function Card Serial Number High Register                                                            | 51 |

| 5.27.          | FCSERL – Function Card Serial Number Low Register                                                             | 52 |

| 6. TEC         | HNICAL SPECIFICATION                                                                                          | 53 |

| 7. THE         | VXIPLUG&PLAY DRIVER                                                                                           | 55 |

|                |                                                                                                               |    |

| 8. PRC         | OGRAMMING THE PRODAQ 3424                                                                                     | 55 |

## Table of figures

| Figure 1 – Removing the ProDAQ module cover                                              | 9   |

|------------------------------------------------------------------------------------------|-----|

| Figure 2 – The ProDAQ module assembly                                                    |     |

| Figure 3 – Simplified block diagram of 3424 function card                                |     |

| Figure 4 – Configuration of analog front-end circuitry (single channel) of the 3424 card | .14 |

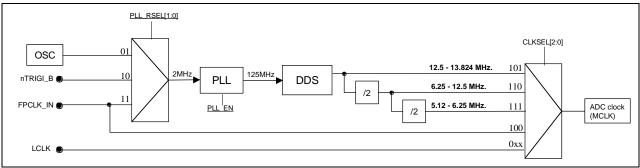

| Figure 5 – ADC clock configuration                                                       | .20 |

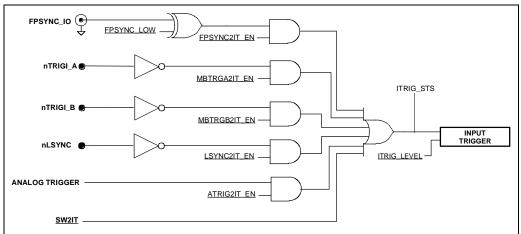

| Figure 6 – Input Trigger configuration scheme                                            |     |

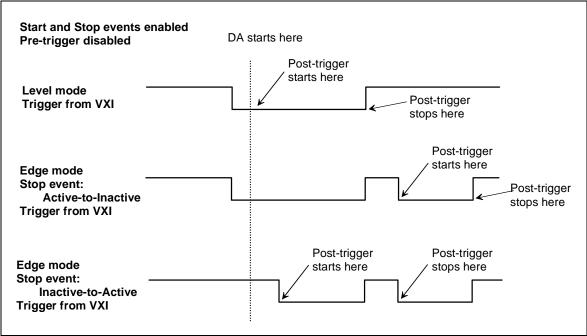

| Figure 7 – Examples of the Input Trigger configuration                                   |     |

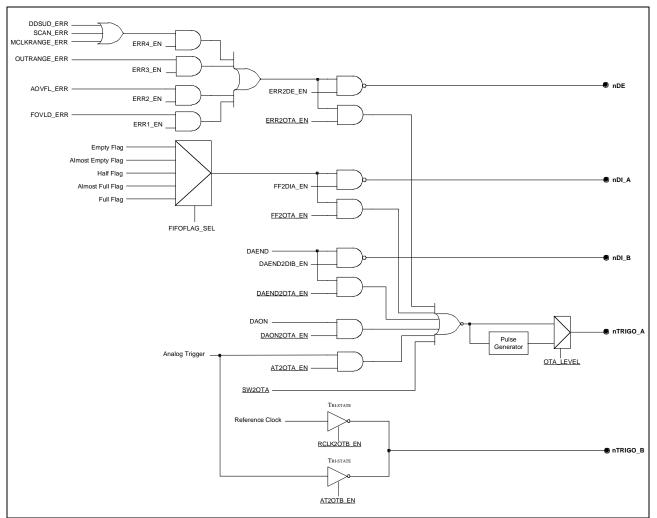

| Figure 8 – Output Trigger, Direct Interrupt and Direct Error configuration scheme        |     |

| Figure 9 – Analog Trigger modes explanation                                              | .24 |

| Figure 10 – The series of the pulses on SYNC/TRIG signal                                 |     |

| Figure 11 – Multiple boards link scheme                                                  |     |

| Figure 12 – Front panel connectors layout                                                |     |

## **Reference Documents**

| Title                   | Number     |

|-------------------------|------------|

| ProDAQ 3120 User Manual | 3120-XX-UM |

| ProDAQ 3150 User Manual | 3150-XX-UM |

|                         |            |

## Glossary

| ADC   | : | Analog-to-Digital Converter                                        |

|-------|---|--------------------------------------------------------------------|

| CRD   | : | Current Regulator Diode                                            |

| DA    | : | Data Acquisition                                                   |

| DAC   | : | Digital-to-Analog Converter                                        |

| DDS   | : | Direct Digital Synthesis                                           |

| DTC   | : | Discharge Time Constant                                            |

| ECL   | : | Emitter-Coupled Logic                                              |

| FIR   | : | Finite Impulse Response digital filter                             |

| FPGA  | : | Field Programmable Gate Array                                      |

| Н     | : | State of the bit(s) defined by hardware (in register description)  |

| ICP   | : | Integrated Circuit Piezoelectric                                   |

| LED   | : | Light Emitting Diode                                               |

| LVDS  | : | Low Voltage Differential Signal(ing)                               |

| РСВ   | : | Printed Circuit Board                                              |

| PGA   | : | Programmable Gain Amplifier                                        |

| PLL   | : | Phase-Locked Loop                                                  |

| RO    | : | Read-only access to register                                       |

| R/W   | : | Read/Write access to register                                      |

| R/WSC | : | Read/Write access to register, Self-Clear after operation finished |

| TEDS  | : | Transducer Electronic Data Sheet                                   |

| VREF  | : | Voltage Reference                                                  |

| VXI   | : | VME eXtensions for Instrumentation                                 |

| WO    | : | Write-only access to register                                      |

|       |   |                                                                    |

### 1. Introduction

The ProDAQ 3424 function card is an 8-channel, 24-bit Sigma-Delta Analog-to-Digital converter function card. It is an add-on card to use together with ProDAQ 3120 and 3150 motherboards. It provides the following features:

- 8 analog channels of simultaneous sampling with 24-bit resolution

- Differential and single-ended analog input configuration

- Max. Input Range ±10V

- Programmable gains of 1, 2, 5, 10, 20, 50, 100, 200, 500 and 1000

- DC/AC coupling

- Variable sampling clock with a maximum 216 kHz output word rate

- Software selectable x10 and x100 decimation for output word rate as low as 200 Hz

- On-board FIFO of 64 ksamples

- Possibility of multiple 3424 cards synchronization (Master/Slave approach)

- ICP® sensor conditioning

- IEEE 1451.4 (TEDS) Smart Transducer Interface support

## 2. Installation

#### 2.1. Unpacking and Inspection

The ProDAQ module is shipped in an antistatic package to prevent any damage from electrostatic discharge (ESD). Proper ESD handling procedures must always be used when packing, unpacking or installing any ProDAQ module, ProDAQ plug-in module or ProDAQ function card:

- Ground yourself via a grounding strap or similar, e.g. by holding to a grounded object.

- Discharge the package by touching it to a grounded object, e.g. a metal part of your VXIbus chassis, before removing the module from the package.

- Remove the ProDAQ module from its carton, preserving the factory packaging as much as possible.

- Inspect the ProDAQ module for any defect or damage. Immediately notify the carrier if any damage is apparent.

#### 2.2. Reshipment Instructions

Use the original packing material when returning a ProDAQ module to Bustec Production Ltd. for calibration or servicing. The original shipping carton and the instrument's plastic foam will provide the necessary support for safe reshipment.

If the original anti-static packing material is unavailable, wrap the ProDAQ module in anti-static plastic sheeting and use plastic spray foam to surround and protect the instrument. Reship in either the original or new shipping carton.

#### 2.3. Preparing the ProDAQ Module

To install a ProDAQ function card into one of the ProDAQ motherboards, you need to remove the module's top cover:

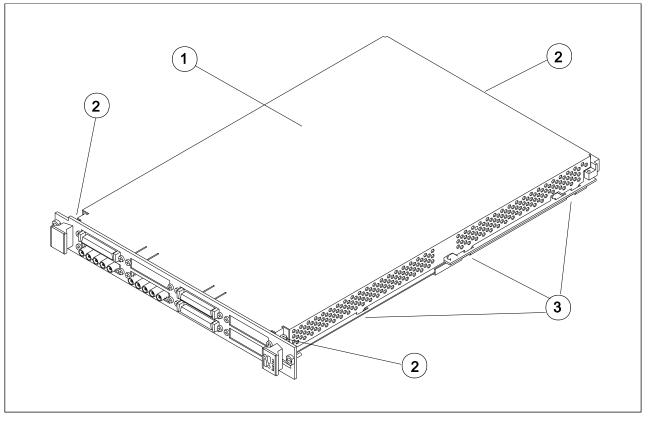

1 - Module Cover

2 - Cover Screws 3 - Cover Hooks

Figure 1 – Removing the ProDAQ module cover

To remove the top cover, remove the one countersunk screw in the back and the two panhead screws towards the front panel (2), that hold the cover in place. Remove the cover by sliding it out of its position towards the VXIbus connectors and up. Take special care about the hooks (3) holding it in place. Try not to lift the cover straight up. See Figure 1 for the location of the screws.

To re-install the cover, slide it back into its position by placing the small hooks over their holes and moving the cover down and forward. Secure the top cover using two panhead screws and one countersunk screw (<sup>(2)</sup>).

#### 2.4. Installing a ProDAQ Function Card

The single-width ProDAQ function cards are arranged inside the ProDAQ module in four stacks of two cards each. The double-width ProDAQ function cards are arranged inside the ProDAQ module in two stacks of two cards each. The function cards are mounted face down, e.g. the front-panel connectors as well as the motherboard connectors are underneath the PCB. Single-width and double-width ProDAQ function cards can be mixed in the ProDAQ module. The 3424 function card is a double-width card.

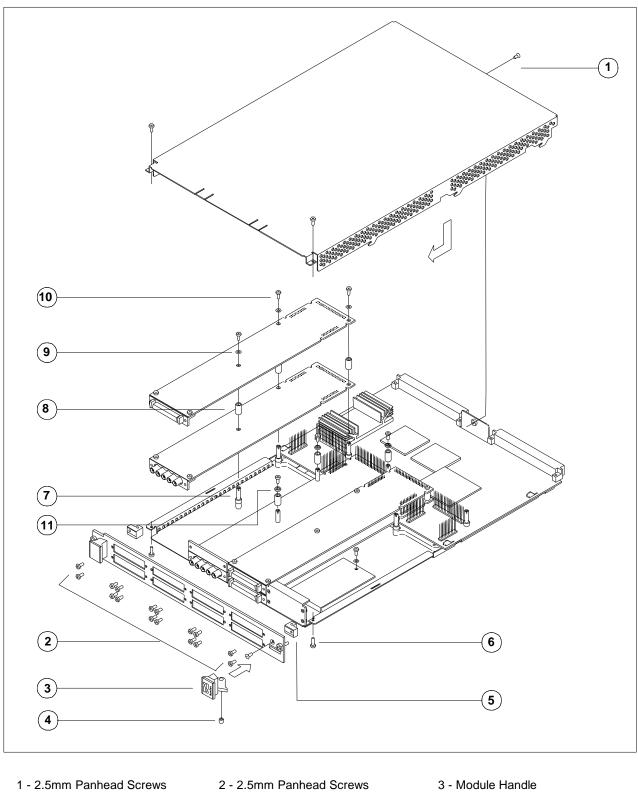

To install a single-width ProDAQ function card in any of the possible positions, use the following procedure (See Figure 2 for reference):

- Remove the top cover of the module as described earlier in this chapter (Fig. 2, Pos. 1).

- Remove all screws on the front-panel holding installed function cards or double filler panels in place (Fig. 2, Pos. 2). Screws holding single filler panels don't need to be removed.

- Remove the two panhead screws that mount the front panel to the modules bottom cover (Fig. 2, Pos. 6).

- Please take special care of the module handles and the rings (Fig. 2, Pos. 3 and 4), which are also fixed by those screws. The mounting angle (Fig. 2, Pos. 5) stays fixed to the front panel.

- Remove the front panel by moving it forward carefully so as to avoid bending the installed function cards.

- Choose the stack and position (lower or upper) where you want to mount the function card. If the stack, in which the function card should be installed, is covered by a double filler panel, you have to remove it before installing the function card.

- Remove the three 2.5mm panhead screws and the crinkle washers from the stack's standoffs (Fig. 2, Pos. 9 and 10 for example).

- If you want to install a function card in the upper position of a stack without having a function card in the lower position, you need to mount both spacers (Fig. 3, Pos. 11) on each standoff. If the stack is already populated with a function card in the lower position, mount only the bigger spacer (Fig. 2, Pos. 8) onto each standoff.

- Place a bayonet (supplied) on each standoff. Align the function card over these and slide carefully down. The function card should be held parallel to the modules bottom cover all the time during its way down.

- Fix the function card by mounting the three 2.5mm panhead screws and the crinkle washers onto each standoff. If you install a function card in the lower position of a stack, you need first to mount both spacers (Fig. 2, Pos. 11) onto each standoff.

- Re-mount the modules front-panel. If there is only one function card mounted in a stack, cover the remaining opening in the front panel by a single filler panel.

- Re-mount the modules top cover.

Adjust the procedure respectively for a double-width ProDAQ function card.

4 - Ring

- 7 Standoff

- 5 Mounting Angle

- 8 Spacer

- 10 2.5mm Panhead Screw

- 11 2mm Spacer

- Figure 2 The ProDAQ module assembly

- Copyright, © 1998-2005 Bustec Production Ltd.

6 - 2.5mm Panhead Screws

9 - Crinkle Washer

#### 2.5. Removing a ProDAQ Function Card

Removing a ProDAQ function card is exactly the reverse operation then installing it. After removing the top cover and the front panel as described previously, remove the three roundhead screws that fix the function card(s) on the standoffs.

Take special care when removing the function card(s) not to bend the motherboard connectors.

After removing the function card(s), install the correct combination of spacers on the standoffs. If a stack is populated with only one function card, each of the standoffs needs to be mounted with both spacers to cover the distance between the cards as well as the PCB thickness of the missing card. If a stack is populated with two function cards, only the bigger spacer must be mounted.

Fix any remaining function cards again by mounting the three panhead screws on the standoffs, remount the front panel and the modules cover.

## 3. Theory of Operation

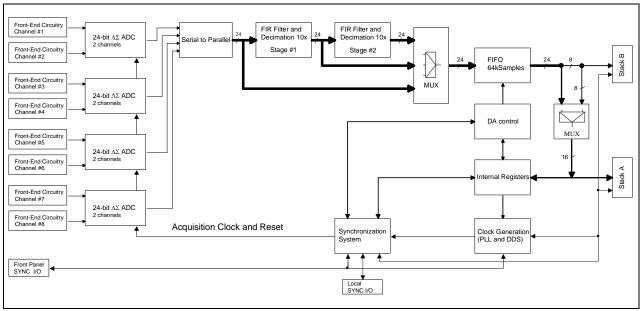

A simplified block diagram of 3424 function card is shown on Figure 3. A brief description of the most important blocks and available functionality follows.

Figure 3 – Simplified block diagram of 3424 function card

#### 3.1. Analog Front-End Circuitry

#### 3.1.1. Analog Front-End general description

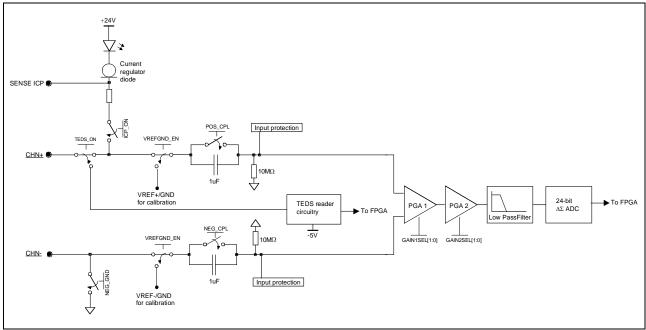

The front-end of the 3424 card gives the user a flexible solution for a wide range of applications. It is designed to accept either single-ended or differential input signals with a bandwidth of up to 100 kHz. The input signal can be either AC or DC coupled. The full-scale range of the card is  $\pm$ 10V. For higher input voltage levels (up to 100V maximum), it is possible to have a factory set attenuator stage.

As well as the standard sensor interface, the card includes the possibility of direct interfacing with ICP sensors and accessing the sensors' Transducer Electronic Data Sheet (TEDS) information. The constant current power source is provided on the board. A LED lights when ICP is selected and drawing current, so it simplifies system setup and detection of open circuits.

For calibration purposes, the input of every channel can be connected to the voltage output of the high-precision ProDAQ 3201 voltage reference board by switching with relays. This voltage reference board can be programmed to 0V (ground connection). The card has built-in input overvoltage protection diodes designed to prevent damage being caused to the input programmable gain amplifier (PGA) stage.

The input signal goes to the PGA stage. The possible gain values are: 1,2,5,10,20,50,100,200,500 and 1000, thus providing immense flexibility for the user. The output of the gain stage is fed to a 4 pole fixed Butterworth anti-aliasing analog input filter which allows for output sample rates in the range of 20 kHz to 216 kHz without violating Nyquist theorem (sampling rates as low as 200 Hz can be achieved with implemented in FPGA digital filters and decimation stages). The output of the filter after offset correction is fed to the differential input of the ADC. Single channel configuration of the 3424 card front-end circuitry is shown on Figure 4.

Figure 4 – Configuration of analog front-end circuitry (single channel) of the 3424 card

#### 3.1.2. ICP sensor conditioning

An ICP sensor requires a constant current bias. This is generated using a Current Regulator Diode (CRD) connected to +24V. For a +24V supply the sensor output will then bias at about +10V with  $\pm$ 10V max swing. The accuracy of the current source is not critical although it needs to be constant. At high frequencies ICP sensors require higher current in order to operate with the same cable length. The maximum frequency is proportional to the current & inversely proportional to the cable capacitance (i.e. cable length). Thus, the 3424 is fitted with one 4.7mA CRD as a standard with the second one fitted upon request.

The ICP excitation current is switched to the ICP sensor with a relay. If ICP is selected and the ICP excitation current is flowing then a LED lights to indicate this. Because it often happens that the sensor do not connect directly to the VXI module, but to some external signal conditioning unit or breakout board, it is desired that the ICP current can be indicated in this remote location. This can be achieved with additional SENSE ICP signal routed to the front panel SCSI connector. Comparing voltage drop across  $22\Omega$  sense resistor with a reference voltage level allows switching on a LED diode in the signal conditioning unit when the ICP excitation current is really flowing. Other solutions, like digital control of a remote LED, don't allow for detection of open circuit in this case.

The positive output of the ICP sensor connects to the positive input of the channel. During normal operation, the signal is AC coupled in order to remove the DC bias. The negative side of the ICP sensor needs to be connected to the same GND as the +24V supply. For the 3424 card this is achieved with means of a relay that can switch the negative side to GND for single-ended sensors.

At low frequencies there are two important considerations. One is the Discharge Time Constant (DTC) of the sensor. This varies from sensor to sensor and can be from milliseconds to several hundreds of seconds. The user needs to consider this effect when measuring signals.

The second low frequency effect is the time constant of the coupling circuit when used in AC coupling mode. A  $10M\Omega$  resistor with a  $1\mu$ F coupling capacitor requires 50 seconds to reach 5RC (5 time constants), required for drift free stable operation.

#### 3.1.3. TEDS reader interface

Transducer Electronic Data Sheet (TEDS), is a nonvolatile memory within a sensor that is utilized for storing information about that sensor. The manufacturer of the sensor deposits, into this memory, initial information such as manufacturer name, sensor type, model number, serial number, and calibration data. Memory space allocation permits the user to add additional information such as channel ID, location, position, direction, tag number, etc. The protocols and formats of the data are defined by IEEE P1451.4 standard.

The sensor operates in a "mixed mode", i.e. analog or digital fashion. In the digital mode, the information stored in memory is downloaded. In the analog mode, the sensor functions normally, as a measurement device. A suitable TEDS signal conditioner is used to access the memory digitally, over the same wires ordinarily used for analog measurement signal transmission.

The 3424 card has a common TEDS reader interface circuitry for all eight channels. A relay in the positive input of the channel is used to connect it to a TEDS reader. Care should be taken not to write the software in the way that connects more than one channel to the TEDS reader at a time.

#### 3.2. Digital Front-End Circuitry

#### 3.2.1. Motherboard $\leftrightarrow$ function card interface

This is the interface that is used to exchange data between motherboard and function card. Detailed description of this interface is beyond the scope of this manual. However, a short explanation is needed regarding names used. Following names appear interchangeably throughout document:

- Trigger input, Stack A  $\leftrightarrow$  nTRIGI\_A

- Trigger input, Stack B  $\leftrightarrow$  nTRIGI\_B

- Trigger output, Stack A ↔ nTRIGO\_A

- Trigger output, Stack B ↔ nTRIGO\_B

- Direct Interrupt, Stack A ↔ nDI\_A

- Direct Interrupt, Stack B ↔ nDI B

- Direct Error ↔ nDE

The shorter names are used on the drawings for better clarity. The small "n" in the beginning of the name indicates that the signal is active low level.

#### 3.2.2. Front panel digital signals

There are three SMB type connectors on the front panel of the card.

The connectors are:

- FPSYNC\_IO, bi-directional Input/Output for distribution of SYNC/TRIG signals in TTL standard. When configured as an input, the active polarity is software selectable. When configured as an output, it is always active low level.

- FPCLK\_IN, clock input in ECL standard, with software programmable termination (50 $\Omega$  to 2V)

- FPCLK\_OUT, clock output in ECL standard

Care should be taken while making cable connections between multiple cards. First of all, it is important that the cables used for clock and SYNC/TRIG signals are of the same length. Big difference in cable length could lead to a change in their phase relationship. As a result, the Master

and Slave cards could sample analog signal on different clock edges. Cables should be kept as short as possible. This is important when phase performance is critical. It is worth to remember that the cable adds approximately 6 ns delay per meter. Also it is important that the optimal way of connecting fast digital signals in respect for their integrity is point-to-point connection. If it is impossible, the stubs should be kept as short as possible. Note that the termination on the ECL signal should be enabled only on the last receiver in the chain. To avoid stubs, clock forwarding mechanism was implemented on 3424 card. It works in the way that the card that receives clock on the terminated FPCLK\_IN input simultaneously outputs it on FPCLK\_OUT output. This output can be connected to the input of another 3424 card, and so on. Clock forwarding requires setting bits FPCLKO\_SEL in MODE2 register to '11'.

#### 3.2.3. Local synchronization link

There is possibility of synchronization of multiple 3424 cards in the same VXI module with local cable connections between them (local synchronization link). This makes possible to distribute clock and SYNC/TRIG signals without propagating them through switch matrix on the motherboard (trigger output lines can be used not for synchronization, but to generate interrupts to the host). For this purpose, two special flex cable connectors are fitted in the middle of the board. The cables necessary to make local link connection are available from Bustec. Note that the cables have contacts only on one side, so care must be taken to insert them properly to the connector. Clear indications of cable orientation are printed on the 3424 card.

The local synchronization signal (nLSYNC) is distributed in TTL standard (single line with open collector drivers). Local clock (LCLK) signal, in order to ensure its high quality, is distributed in LVDS standard. The local synchronization link is designed in the way that ensures automatic termination of the LVDS transmission line on the last card in the local synchronization chain. As a result, there are some limitations on Master/Slave card positions in VXI module when local synchronization link is used – the Master must be the first card in the local synchronization chain. Master can be on either of the stacks, but the Slaves can be only on stacks that are down the chain. The stack order is: stack 1-2  $\rightarrow$  stack 5-6  $\rightarrow$  stack 7-8  $\rightarrow$  stack 2-3.

#### 3.3. Data Acquisition

The Data Acquisition (DA) on the 3424 is a process of acquiring the samples and storing them in the memory. The samples can be acquired as a pre-trigger and post-trigger data. Before samples becomes valid for the pre-trigger and post-trigger, the process of updating clock generation circuitry (DDS), resetting ADCs and settling FIR filters have to take place.

The Data Acquisition is controlled by the state machine on the board. This state machine can be in one of the following states, which determines the state of the Data Acquisition:

| STEP | STATE                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1    | IDLE<br>(IDLE_ST)             | All needed settings (front-end configuration, clock and trigger selection, Data Acquisition modes) must be done in this step                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2    | DDS UPDATE<br>(DDSUD_ST)      | Card is brought to this state with the ARMING command if SYNC_NEED bit has been asserted. In this state, the card performs the update of the DDS settings. If the board is a Master then it updates DDS automatically. In the case of a Slave, it waits for the update pulse generated by the Master and distributed over SYNC/TRIG line.<br>This state is skipped if the Arming command is launched with the SYNC_NEED bit cleared.                                                                                                             |

| 3    | ADC SYNC<br>(ADCSYNC_ST)      | After DDS UPDATE is done, the card performs reset and thus<br>synchronization of the ADCs. Similarly to the DDS update, the<br>Master synchronizes the ADCs automatically while the Slave<br>waits for the synchronization pulse from the Master. The ADCs<br>reset and FIR filters settling takes approximately 900ms. At the<br>end of the process, the Slave gets from the Master another<br>pulse, which causes them to proceed to next state.<br>This state is skipped if the Arming command is launched with the<br>SYNC_NEED bit cleared. |

| 4    | READY FOR DA<br>(READY4DA_ST) | After synchronisation is done, the hardware is ready to start Data<br>Acquisition. It can either start immediately, or wait for the trigger.<br>In addition, the card can be configured to acquire the pre-trigger<br>before the post-trigger phase.<br>When no pre-trigger and 'start on trigger' is selected, the state<br>machine stays in READY4DA_ST state as long as the trigger is<br>not asserted.                                                                                                                                       |

| 5    | PRE-TRIGGER<br>(PRET_ST)      | If the pre-trigger has been enabled, the card starts to collect pre-<br>trigger data. The amount of the scans to collect is defined in the<br>PRET_NOS register. The number of the pre-trigger samples<br>must not exceed the FIFO size.                                                                                                                                                                                                                                                                                                         |

| 6    | POST-TRIGGER<br>(POSTT_ST)    | Post-trigger samples are stored in the FIFO as long as the end of<br>the Data Acquisition does not happen. The Data Acquisition can<br>be ended either after a set number of the scans is collected or<br>after stop trigger event. In this state, it is possible emptying FIFO<br>on-the-fly for acquisitions longer than the FIFO size.                                                                                                                                                                                                        |

Table 1 – States of the Data Acquisition state machine

#### 3.3.1. Data Acquisition modes

Data Acquisition is a process of storing samples from ADCs in the FIFO. When the ADCs and filters have settled (synchronization is done), the board is ready to start Data Acquisition. Data Acquisition is composed of the pre-trigger and post-trigger. It can be configured to skip the pre-trigger.

The pre-trigger, if enabled, starts immediately after synchronization is done. The 3424 card collects specified number of scans (PRET\_NOS register) and stores them in the FIFO. The number of the pre-trigger samples (number of the scans multiplied by number of the channels enabled for the Data Acquisition) cannot be bigger than the size of the FIFO, as the readout of the FIFO (emptying the FIFO) is prohibited in this state. When the required number of the scans is collected, the pre-trigger is done but the board stays in the pre-trigger state as long as the conditions to start the post-trigger are not fulfilled. In this case, every new scan added to the FIFO causes the oldest scan to be dropped.

In some cases, the pre-trigger can be ended before the set number of the scans is collected. This can happen if the trigger can be accepted before the pre-trigger is finished (PRET\_REJECT bit cleared) and start trigger event took place. If the user wants to collect the entire specified pre-trigger, the PRET\_REJECT bit has to be set. In this case, triggers coming before completion of the pre-trigger are rejected.

If the pre-trigger is ended before completion, then the PRET\_NOS register readout returns the number of scans left to complete.

The post-trigger starts when the start condition is met. The start condition is selected with the DA\_STARTSEL bit. The following ways can be selected:

- Post-trigger starts immediately after the ADCs and filters are settled (if pre-trigger has been disabled) or after pre-trigger is done (if the pre-trigger has been enabled)

- After the trigger event happens

The post-trigger ends when the Data Acquisition stop condition is met. The stop conditions of the Data Acquisition are as follows:

- Selected number of scans has been collected (DA\_STOPSEL bits set to '00')

- Stop trigger happens (DA\_STOPSEL bits set to '01')

- Software stop (DA\_SKIP or SW\_RST bits set)

- Error happens (if STOP\_ON\_ERR bit set and any error enabled)

Up to 16,777,215 post-trigger scans can be set in the POSTT\_NOSL/H registers. The unlimited number of samples can be achieved by setting stop mode to DA\_SKIP (DA\_STOPSEL bits set to '10').

#### 3.3.2. Data storage and readout

The samples are stored in the on-board FIFO memory. The depth of the FIFO is 64 ksamples (optionally it can be 128 ksamples). The samples are stored scan-by-scan, with the channel data interleaved within the scan (channel with the lower number goes first). The scan is composed of one to eight channels

The write to the FIFO is always 32-bit wide. The write can be performed by the motherboard during idle state (FIFO\_WRL/H registers) or by the ADCs during Data Acquisition. The 24-bit data from the ADC is extended to the 32-bit, two's complement format.

The readout from the FIFO can be either 16-bit or 32-bit wide, which is selected using FIFO\_16B bit. The readout initiated by the motherboard is disabled in the pre-trigger mode.

The two read out modes from the FIFO memory are:

- 16-bit readout: motherboard in the first access reads the 16 least significant bits from the FIFO, the following access is used to read 16 most significant bits. This mode is supported on both, 3120 and 3150 motherboards

- 32-bit readout: two stacks (A and B) are used to read all 32 bits in one access. This mode is supported only on 3150 motherboard and improves the throughput significantly when emptying FIFO on-the-fly.

The FIFO memory chip outputs five status flags:

- 1) empty flag

- 2) almost empty flag

- 3) half flag

- 4) almost full flag

- 5) full flag

Full

0

0

0

0

0

1

The flags are used to control the number of the samples stored in the FIFO when emptying this memory. The status of the FIFO flags can be read directly (FIFO\_CTRL register) or selected flag (only one) can be directed to the Output Trigger or Direct Interrupt. The following table defines the FIFO flag assertion:

Almost Empty Almost Full Empty Number of samples in FIFO Half 64 ksamples FIFO 128 ksamples FIFO 0 0 1 1 0 0 1 to (n+1) 1 to (n+1) 0 1 0 0 0 (n+2) to 32769 (n+2) to 65537 0 0 0 32770 to (65536-m) 65538 to (131072-m) 0 0 1 0 (65537-m) to 65536 (131073-m) to 131072 0 0 1 1

131073Table 2 – FIFO flag thresholds

0

0

1

1

The offsets: **n** and **m** are programmable. Their default value (after FIFO master reset) is 255. They can be updated using FIFO\_WRL/H registers (bits used: 16 LSB bits for 64 ksamples FIFO and 17 LSB bits for 128 ksamples FIFO) if the FIFO\_LD bit has been set. The first access stores **n** offset, the second access stores **m** offset, then the sequence repeats.

The FIFO master reset (FIFO\_MRS bit) has to be performed during the board initialisation. Afterwards, the partial reset is sufficient to reset the FIFO as it resets the pointers only.

#### 3.3.3. FIR filters and decimation

65537

To achieve even lower output sampling rates with the same fixed analog filter, two decimation stages by 10 are implemented in FPGA. Internal multiplexer in the FPGA allows for selection which data is to be stored in the FIFO. Either not decimated samples, samples decimated by 10 (one decimation stage), or samples decimated by 100 (two decimation stages) can be selected. However, such selection applies to all channels, i.e. all channels must work with the same output sampling rate. With such approach, output sample rate of the card spreads from as low as 200Hz to 216kHz.

Theoretical passband frequency of FIR filter spreads from 0.08  $\pi$  rad / sample (0.04 of the FIR input sample rate). The frequency response is extremely flat in this area and has ripple of only 2.5µdB. Stopband starts at 0.1  $\pi$  rad / sample (0.05 of the FIR input sample rate) with attenuation of 126dB. Very narrow transition band and high requirements to the ripple and attenuation values resulted in filter order of 802. Symmetrical coefficients ensure linear phase response in the passband.

To minimize effects of fixed point arithmetic implementation (quantization error), 28-bit coefficient length is used.

#### 3.3.4. Sampling settings

To start Data Acquisition, ADC sampling clock selection and ADC output speed rate has to be setup.

The sampling clock can be generated on the board out of the reference clock (2 MHz) or it can be received from the external generator (for example from the other Master) as a target ADC sampling clock.

When generating ADC clock on the board, a 2 MHz reference clock can be taken from one of these sources:

- Local 2 MHz oscillator

- Reference clock received through the stack B trigger input line and a switch matrix on the motherboard from another ProDAQ function card

- Reference clock received through the front panel from another function card or other external clock source

This reference clock is used then to produce 125 MHz DDS input clock. DDS circuitry is used to synthesise the clock in the range from 12.5 MHz to 25 MHz. Together with two additional frequency dividers (the reason for them is jitter performance optimisation outside main DDS octave) it allows for generation of any ADC clock in the range of 5.12 MHz to 13.824 MHz. The Table 3 shows the DDS configuration and the corresponding ADC clock frequencies.

| CLKSEL | ADC clock [MHz] |

|--------|-----------------|

| 111    | 5.12 – 6.25     |

| 110    | 6.25 – 12.5     |

| 101    | 12.5 – 13.824   |

|        | 111<br>110      |

Table 3 – DDS settings for the required ADC clock frequency

The details on the DDS frequency programming can be found in DDS\_WX register description. In addition to the on-board generator, the target ADC clock can be taken from front panel clock input as well as from local synchronization link clock line. Figure 5 shows the ADC clock configuration scheme.

Figure 5 – ADC clock configuration

The possible output word rates for the given ADC clock and speed settings are shown in Table 4.

| ADC clock     | ADC SPEED       | Output word rate [kHz] |               |                |

|---------------|-----------------|------------------------|---------------|----------------|

| [MHz]         | (over-sampling) | Decimation=Off         | Decimation=10 | Decimation=100 |

| 5.12 – 13.824 | Normal (x128)   | 20 – 54                | 2.0 – 5.4     | 0.2 – 0.54     |

| 5.12 – 13.824 | Double (x64)    | 40 – 108               | 4.0 – 10.8    | 0.4 – 1.08     |

| 5.12 – 13.824 | Quad (x32)      | 80 – 216               | 8.0 – 21.6    | 0.8 – 2.16     |

Table 4 – ADC output word rates

For the overlapping regions of the output word rate use the option with the higher over-sampling for better performance.

#### 3.3.5. Input Trigger

Input Trigger can be used to start or to stop collecting post-trigger data, depending on the Data Acquisition start/stop mode. The following Input Trigger sources are available:

- Trigger from the switch matrix on the motherboard, stack A

- Trigger from the switch matrix on the motherboard, stack B

- Trigger from the front panel

- Trigger from the local synchronization link

- Analog trigger

- Software trigger

Any number of the sources listed above can be selected at the same time.

The Input Trigger configuration scheme is shown on Figure 6.

Figure 6 – Input Trigger configuration scheme

Input Trigger is used only if the 3424 is configured as a Master, otherwise Input Trigger stays in reset and the function card is controlled by the synchronization pulses coming from a remote Master.

Input Trigger logic detects two events on the trigger source lines that can be used to start or to stop the Data Acquisition depending on the DA\_START\_SEL and DA\_STOP\_SEL bits settings. Input Trigger reacts on edge or on level. The edge requires the transition while the level requires the state. Selection of the edge/level mode is common for the start and the stop events.

Table 5 shows the definition of the start and stop events.

| MODE                    | START EVENT                   | STOP EVENT                                                                                                          |

|-------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Level (ITRIG_LEVEL='1') | Active state                  | Inactive state                                                                                                      |

| Edge (ITRIG_LEVEL='0')  | Inactive-to-Active transition | Active-to-Inactive transition<br>when STOPTRIG_ESEL='0',<br>Inactive-to-Active transition<br>when STOPTRIG_ESEL='1' |

Table 5 – Input Trigger start and stop events

Active state of the triggers coming from the VXI backplane / switch matrix and from the local synchronization link is always low. Active state of the front panel source is software selectable (FPSYNC\_LOW bit).

Input Trigger can be accepted when the Data Acquisition is ready to be started. During IDLE, DDS UPDATE and ADC SYNC states Input Trigger logic rejects coming trigger events. Examples of the Input Trigger configuration are shown on Figure 7.

Copyright, © 1998-2005 Bustec Production Ltd.

Figure 7 – Examples of the Input Trigger configuration

#### 3.3.6. Output Trigger, Direct Interrupt and Direct Error

Output Trigger, Direct Interrupt and Direct Error provide the way of sending out the information about some events, which occur on the 3424. Because of the fact that the 3424 is double width function card, two trigger outputs are available as well as two Direct Interrupts and one Direct Error. The sources of the trigger and interrupts are listed below:

- 1) Trigger output, stack A:

- FIFO flag

- Error flag

- Analog trigger

- Data Acquisition On (DA\_ON) flag

- Data Acquisition End (DA\_END) flag

- Software generated trigger

- 2) Trigger output, stack B (only one source can be enabled for this trigger):

- Reference clock

- Analog trigger

- 3) Direct Interrupt, stack A:

- FIFO flag

- 4) Direct Interrupt, stack B:

- Data Acquisition End (DA\_END) flag

- 5) Direct Error, stack A:

- Error flag

Note that after arming command, no new FIFO flag triggers/interrupts are generated until card reaches post-trigger state. This is to allow for collecting more pre-trigger scans than the selected FIFO threshold without generating an interrupt, so that the FIFO flag trigger/interrupt will be generated only when there is data in the FIFO that can be read (reading from FIFO is forbidden when the card is in pre-trigger state).

Stack A is always an odd stack number of the stacks occupied by the function card while stack B is an even stack number. Figure 8 shows the configuration scheme of all output signals.

Figure 8 – Output Trigger, Direct Interrupt and Direct Error configuration scheme

The Output Trigger can be generated as a pulse or as level. If the level has been selected the Output Trigger stays active as long as the source of the trigger is active. If the active time is shorter than 200ns then the function card keeps the trigger asserted for this time. For the pulse settings, the pulse of 200ns is generated every time the source of the trigger becomes active.

Direct Interrupt is used to send the interrupt to the LIST processor on the ProDAQ 3150 motherboard without using the trigger output line. The LIST processor reaction to the Direct Interrupt is much faster than the reaction to the trigger line so this feature is very useful when for example emptying FIFO on-the-fly is needed. Direct Interrupt line can be used only when 3424 function card is used together with 3150 motherboard.

Direct Error can be used only when 3424 function card works together with 3150 motherboard. Lower and upper stack share the same Direct Error line so after error was set the software has to detect which board generated Direct Error by polling FCCSR register. There are following error sources on the 3424 board:

There are following error sources on the 3424 board:

- DDS update error (DDSUD\_ERR) happens if the board is a Slave and the external SYNC/TRIG pulse is not in phase

- Scan error (SCAN\_ERR) happens if the samples from the ADC comes too often. This

might be caused by the higher than allowed ADC clock frequency

- ADC clock out-of-range error (MCLKRANGE\_ERR) happens if the ADC clock frequency is outside of the required range (5.12 MHz to 13.824 MHz)

- Input signal out-of-range error (OUTRANGE\_ERR) happens if the input signal is out of range for selected gain (±10V for gain=1, ±5V for gain=2, etc.)

- Arithmetic overflow error (AOVFL\_ERR) happens if the arithmetic overflow in the gain correction or FIR filter occurs. Note that the output sample in this case gets saturated to Full Scale (positive or negative, depending in which direction arithmetic overflow happened)

- FIFO overload error (FOVLD\_ERR) happens if the FIFO is full and next samples is ready to be written

#### 3.3.7. Analog Trigger

Analog Trigger is useful in acquiring transient signals by nature, e.g. vibrations after striking beam with a hammer.

If enabled, Analog Trigger is generated when the input signal in the chosen analog channel meets specified conditions. Analog Trigger can be used as a source of the on-board Input Trigger or it can be selected as a source of the Output Trigger and forwarded further to remote Master.

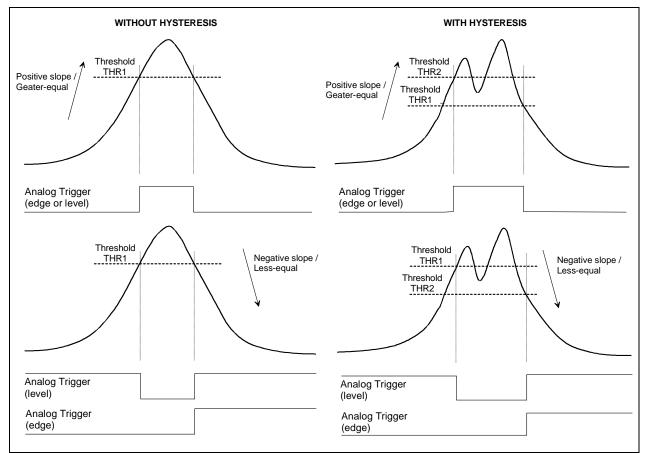

There are two Analog Trigger modes: edge and level (see Figure 9). Both can be specified as "positive slope/greater-or-equal" or "negative slope/less-or-equal" directions. In the edge mode the signal must cross the specified threshold while for the level it is not required and thus the difference between the edge and level might happen only when the Data Acquisition starts.

The Analog Trigger can be programmed with or without hysteresis. When the hysteresis is not required, only one threshold has to be defined, THR1. For the hysteresis mode, two thresholds have to be defined, THR1 and THR2. In hysteresis mode, THR1 has to be crossed first independently on the selected direction.

Figure 9 – Analog Trigger modes explanation

Any channel signal can be selected as a source of the Analog Trigger, however only one channel can be selected at a time. The Analog Trigger is implemented in the digital domain and the thresholds are programmable with 12-bit resolution.

#### 3.3.8. Analog channel correction

The board provides the correction of the analog channel offset and gain.

The offset correction is done with the DAC. To calibrate an offset, the channel input (both positive and negative paths) must be grounded. To achieve that, the software should set VREFGND\_EN bit for selected channel to '1' and reset VREF\_ON bit in MODE2 register to '0'. A value for the offset DAC should be set to 0x8000 and an ADC value shall be read (OFFMIN). Then a value for offset DAC should be set to 0x8FFF and an ADC value shall be read again (OFFMAX). It is a good practice to acquire a big number of samples (for example 10 000) and then average them to calculate both OFFMIN and OFFMAX. This causes that the calibration process is not affected by noise. The final value of the offset correction coefficient (OFFCOEF) that should be written to offset DAC is calculated as follows:

$1LSBOFF[V] = \frac{OFFMAX[V] - OFFMIN[V]}{4095}$  $OFFCOEF(16bit\_value) = 0x8000 - \frac{OFFMIN[V]}{1LSBOFF[V]}$

Gain correction is performed in digital domain inside FPGA. To calibrate the gain, the known precise voltage needs to be supplied to the channel input. The ProDAQ 3201 voltage reference module can be used for this purpose. The software should set VREFGND\_EN bit for selected channel to '1' and set VREF\_ON bit in MODE2 register to '1'. The ProDAQ 3201 should be programmed to the required voltage. Note that only one channel should be connected to the VREF at a time. ADC value is then obtained (GAINERR). Also in this case it is advised to acquire a big number of samples (for example 10 000) and then average them to calculate GAINERR value. The final 24-bit value of the gain correction coefficient (GCOEF) that should be written to GCOEFL and GCOEFH registers is calculated as follows:

$1LSB[V] = \frac{2 \cdot 10.24[V]}{2^{24}}$

$GCOEF(24bit\_value) = \frac{\frac{VREF[V]}{1LSB[V]}}{GAINERR} \cdot 0x800000$

Offset and gain correction coefficient values can be stored in the EEPROM memory. The on-board EEPROM memory is big enough to accommodate separate offset and gain calibration data for every channel and for every gain. Default offset and gain correction coefficients (for gain=1) are automatically uploaded on the power-up. Calibration coefficients for different gains should be read from EEPROM memory and then written to respective registers by software.

The card is shipped factory calibrated, i.e. with correction coefficients stored in the EEPROM memory for all possible gain selections. For the purpose of calibration in the field by the user, the ProDAQ 3201 voltage reference board is needed.

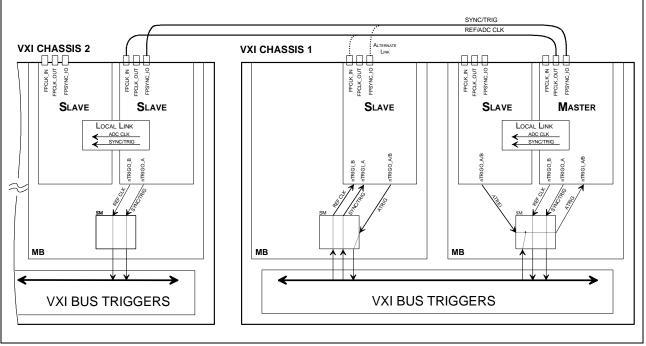

#### 3.3.9. Multiple cards configuration

The 3424 is able to work in the stand-alone mode or in multiple-card synchronization mode.

The multiple-card synchronization mode is used in the case when all 3424 boards have to sample the input signal simultaneously and when Data Acquisition has to start in the same time on all of them.

The 3424 can be set as a Master (MASTER bit in FCCSR register set) or Slave (MASTER bit cleared). If 3424 works in a stand-alone mode then it has to be always a Master. If the group of the 3424 boards work in a multiple-card synchronization mode then only one function card can be set as a Master and all others as a Slaves.

The Master generates two signals that have to be distributed to all Slaves: clock signal and SYNC/TRIG signal.

The clock signal can be distributed as a PLL reference clock (2 MHz low frequency signal multiplied then in the PLL to 125 MHz for DDS circuitry) or as a sampling clock applied directly to the ADCs (5.12 MHz to 13.824 MHz). Depending on the selected clock signal, proper settings on the Slaves have to be done.

The Master is able to send the clock signal to the following outputs:

- 1) PLL reference clock

- Trigger output, stack B

- Front panel clock output

- 2) ADC clock

- Local synchronization link clock line

- Front panel clock output

The configuration of the Master where the reference clock is send to the trigger output and the ADC clock is send to the local synchronization and/or front panel clock outputs is allowed.

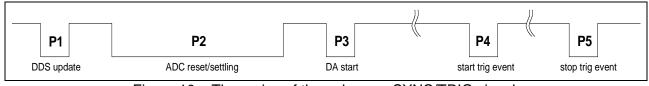

The second signal generated by the Master is SYNC/TRIG signal. It is used to synchronize all ADCs and start Data Acquisition at the same time. The SYNC/TRIG events are described in Table 6.

| PHASE | EVENT                                                                                                                                                                                             | CONDITION                                                                                      | PULSE                                                                                  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| P1    | <b>update of the DDS</b> – this pulse<br>is used by the boards which<br>receive PLL reference clock                                                                                               | Occurs only if the board<br>armed together with the<br>SYNC_NEED bit set                       | P1, width of 200ns                                                                     |

| P2    | <b>reset and settling of the ADCs</b><br>– this pulse resets ADCs and<br>ensures the settling time of the<br>FIR filters                                                                          | Occurs only if the board<br>armed together with the<br>SYNC_NEED bit set                       | P2, width of approx.<br>896ms, synchronized to<br>the falling edge of the<br>ADC clock |

| P3    | start of the Data Acquisition –<br>this pulse tells the Slave to start<br>Data Acquisition (go to pre/post<br>trigger or wait for the start/stop<br>trigger events, depending on the<br>settings) | Always present                                                                                 | P3, width of 5 ADC<br>clocks, synchronized to<br>the falling edge of the<br>ADC clock  |

| P4    | <b>start trigger event</b> – this pulse<br>tells the Slaves to go to the post<br>trigger                                                                                                          | Occurs if the start on<br>trigger selected on the<br>Master and start trigger<br>event happens | P4, width of 2 ADC clocks, synchronized to the falling edge of the ADC clock           |

| P5    | <b>stop trigger event</b> – this pulse<br>tells the Slaves to finish post<br>trigger                                                                                                              | Occurs if the stop on<br>trigger selected on the<br>Master and stop trigger<br>event happens   | clocks, synchronized to                                                                |

Table 6 – SYNC/TRIG signal events

Figure 10 – The series of the pulses on SYNC/TRIG signal

The Master is able to send the SYNC/TRIG signal (active low) to any of these outputs:

- Trigger output, stack A

- Local synchronization link

- Front panel FPSYNC\_IO line

The clock and SYNC/TRIG signals have to be delivered from the Master to the Slaves. There are three possible distribution ways shown in the Table 7.

| Distribution way                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Description                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Local<br>synchronization link                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Local synchronization link connects boards sitting on the same<br>motherboard (up to 3 Slaves connected to the Master). It uses<br>special connectors and cables going across the function cards.                                                              |

| VXI distribution connects 3424 boards residing on the motherboar<br>on the VXI bus to the Master. This distribution way is implement<br>with the VXI triggers. The SYNC/TRIG and clock signals go to<br>trigger outputs on the Master (stack A and B respectively) and the<br>through the VXI trigger lines they are distributed to all Slaves (trig<br>inputs, stack A and B on the Slaves). The clock signal can<br>distributed over VXI bus only as a reference clock (not ADC clock |                                                                                                                                                                                                                                                                |

| Front panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Front panel distribution can be used to connect the Master to the<br>Slaves sitting on the motherboards in the same VXI chassis or in the<br>other chassis. The SYNC/TRIG signal can be distributed over front<br>panel as well a reference clock or ADC clock |

Table 7 – Ways of clock and SYNC/TRIG signal distribution

The simplified link scheme of the multiple 3424 boards synchronization is shown on Figure 11. The synchronisation of the multiple boards requires that settings of the Slaves have to correspond to the settings of the Master. In addition, the arming of the Slave has to occur before the arming of the Master. After the end of the Data Acquisition on the Master, the software has to check if all Slaves finished their Data Acquisition processes.

The Analog Trigger on the Slaves can be used to trigger the Master in the same way as Analog Trigger on the Master. The Analog Trigger from the Slaves has to be linked to the Input Trigger of the Master via VXI trigger lines.

Figure 11 – Multiple boards link scheme

A 3424 card being a Slave can also forward clock and SYNC/TRIG signals to other Slaves. It is useful in multi-chassis VXI systems. The Slave located in the chassis without active Master forwards SYNC/TRIG and clock coming through the front panel to the other Slaves using VXI bus triggers or local synchronization link. Note that only PLL reference clock can be forwarded to the VXI bus triggers. The Slave card in the chassis without active Master can't generate Analog Trigger, since there is simply no way to route it to the Master's chassis.

When synchronizing multiple cards, an inevitable cross channel phase error appears. This happens because of propagation delay of SYNC/TRIG and clock signals. Typical clock phase shift between Master and Slave clock for different link schemes is given in Table 8.

| Synchronization link scheme                              | Typical sampling clock phase shift |

|----------------------------------------------------------|------------------------------------|

| Local synchronization link                               | 8 ns                               |

| Synchronization through the trigger lines, cards on the  | 19 ns                              |

| same motherboard                                         |                                    |

| Synchronization through the trigger lines, cards on      | 36 ns                              |

| different motherboards                                   |                                    |

| Synchronization through the front panel, distribution of | 13 ns                              |

| ADC clock (20 cm long cable)                             |                                    |

| Synchronization through the front panel, distribution of | 18 ns                              |

| reference clock (20 cm long cable)                       |                                    |

Table 8 – Typical clock phase shift between Master and Slave cards.

This phase shift is insignificant for most low-frequency applications, since the signal phase error is proportional to the signal frequency. For example, 36 ns of the Master and Slave clock phase shift corresponds to 0.0026 degree of the cross channel phase mismatch for 200 Hz signal and 0.26 degree for 20 kHz signal.

It is worth to remember that the cable adds approximately 6 ns delay per meter. This needs to be taken into account when external cables are used to connect Master and Slave cards, i.e. when front panel connectors are used to send SYCN/TRIG and clock signals. The values in the Table 8 are valid for 20 cm long cable.

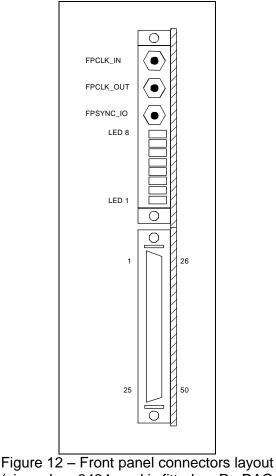

## 4. Front Panel Connectors

The front panel of the 3434 card contains:

- high density, 50 pin, female SCSI type connector used for analog signal connections

- 8 LED diodes to indicate ICP excitation current in respective channel

- 3 SMB connectors for digital signals used for synchronization purposes

The view of the front panel layout is shown on the Figure 12.

(view when 3424 card is fitted on ProDAQ module in VXI chassis)

The signal assignment on the front panel SCSI connector is shown in Table 9. Note that the power supplies (+24V, +15V, +5V, -15V) available on the front panel have limited current load and are available exclusively for supplying signal conditioning boards manufactured or accepted by Bustec.

| Signal       | Pin | Pin | Signal      |

|--------------|-----|-----|-------------|

| +24V         | 1   | 26  | Ground      |

| Cable Shield | 2   | 27  | SENSE ICP 8 |

| CHN8-        | 3   | 28  | CHN8+       |

| +15V         | 4   | 29  | Ground      |

| Cable Shield | 5   | 30  | SENSE ICP 7 |

| CHN7-        | 6   | 31  | CHN7+       |

| +5V          | 7   | 32  | Ground      |

| Cable Shield | 8   | 33  | SENSE ICP 6 |

| CHN6-        | 9   | 34  | CHN6+       |

| -15V         | 10  | 35  | Ground      |

| Cable Shield | 11  | 36  | SENSE ICP 5 |

| CHN5-        | 12  | 37  | CHN5+       |

| Cable Shield | 13  | 38  | Ground      |

| Cable Shield | 14  | 39  | SENSE ICP 4 |

| CHN4-        | 15  | 40  | CHN4+       |

| Cable Shield | 16  | 41  | Ground      |

| Cable Shield | 17  | 42  | SENSE ICP 3 |

| CHN3-        | 18  | 43  | CHN3+       |

| Cable Shield | 19  | 44  | Ground      |

| Cable Shield | 20  | 45  | SENSE ICP 2 |

| CHN2-        | 21  | 46  | CHN2+       |

| Cable Shield | 22  | 47  | Ground      |

| Cable Shield | 23  | 48  | SENSE ICP 1 |

| CHN1-        | 24  | 49  | CHN1+       |

| Cable Shield | 25  | 50  | Ground      |

|    | Cable Shield           | 25      | 50        | Ground               |      |

|----|------------------------|---------|-----------|----------------------|------|

| Та | ble 9 – Signal assignn | nents o | n the fro | ont panel SCSI conne | ctor |

## 5. Register Description

All addresses are given in hexadecimal notation. FC\_ADR is address in the function cards address space. VXI\_ADR is address in VXI address space (refer to the motherboard manual for more details).

| Register Name | FC_  | VXI_  | Acces  | Function                                         |

|---------------|------|-------|--------|--------------------------------------------------|

|               | ADR  | ADR   | s Type |                                                  |

| FCID          | 0    | 0     | RO     | Function card ID register                        |

| FCVER         | 1    | 4     | RO     | Function card version register                   |

| FCCSR         | 2    | 8     | R/W    | Function card control and status register        |

| MODE1         | 3    | С     | R/W    | Mode1 register                                   |

| MODE2         | 4    | 10    | R/W    | Mode2 register                                   |

| OTRI_CFG      | 5    | 14    | R/W    | Output Trigger configuration register            |

| ITRI_CFG      | 6    | 18    | R/W    | Input Trigger configuration register             |

| FIFO_CTRL     | 7    | 1C    | R/W    | FIFO control register                            |

| FIFO_WRL      | 8    | 20    | R/W    | FIFO write low register                          |

| FIFO_WRH      | 9    | 24    | WO     | FIFO write high register                         |

| PRET_NOS      | А    | 28    | R/W    | Number of pre-trigger samples                    |

| POSTT_NOSL    | В    | 2C    | WO     | Number of post-trigger samples, low              |

| POSTT_NOSH    | С    | 30    | WO     | Number of post-trigger samples, high             |

| AT_THR_SIGERR | D    | 34    | R/W    | Analog Trigger threshold / signal error register |

| AT_CTRL       | Е    | 38    | WO     | Analog Trigger control register                  |

| CHN1CFG       | F    | 3C    | R/W    | Channel #1 configuration register                |

| CHN2CFG       | 10   | 40    | R/W    | Channel #2 configuration register                |

| CHN3CFG       | 11   | 44    | R/W    | Channel #3 configuration register                |

| CHN4CFG       | 12   | 48    | R/W    | Channel #4 configuration register                |

| CHN5CFG       | 13   | 4C    | R/W    | Channel #5 configuration register                |

| CHN6CFG       | 14   | 50    | R/W    | Channel #6 configuration register                |

| CHN7CFG       | 15   | 54    | R/W    | Channel #7 configuration register                |

| CHN8CFG       | 16   | 58    | R/W    | Channel #8 configuration register                |

| DDS_WX        | 17   | 5C    | R/W    | DDS control words register                       |

| DAC_DATA      | 18   | 60    | WO     | DAC data register                                |

| DAC_ADDR      | 19   | 64    | R/W    | DAC address register                             |

| TEDS_ACC      | 1A   | 68    | R/W    | TEDS access register                             |

| GCOEFL        | 1B   | 6C    | WO     | Gain coefficient write, bits 150                 |

| GCOEFH        | 1C   | 70    | WO     | Gain coefficient write, bits 2316 and address    |

| EPD           | FA   | 3E8   | R/W    | EEPROM data register                             |

| EPC           | FB   | 3EC   | R/W    | EEPROM control register                          |

| FCSUB         | FC   | 3F0   | RO     | Function card sub-type register                  |

| FCSERH        | FE   | 3F8   | RO     | Function card serial number register, high       |

| FCSERL        | FF   | 3FC   | RO     | Function card serial number register, low        |

| FIFO          | 8000 | 20000 | RO     | Readout of FIFO memory                           |

#### 5.1. FCID – Function Card ID Register

FCID register contains function card identification number. Readout should always give value of 3424H.

| Bit  | Access &<br>Default | Description                                                                                                  |

|------|---------------------|--------------------------------------------------------------------------------------------------------------|

| 15:0 | RO<br>0x3424        | FCID – Function Card ID<br>Function card identification number, 0x3424 for 8-channel, 24-bit Sigma-Delta ADC |

#### 5.2. FCVER – Function Card Version Register

This is function card version register. Readout from this register gives information about PCB revision and FPGA design revision.

| Bit  | Access &<br>Default | Description                                                                                                                                                    |

|------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8 | RO<br>h             | <b>FPGA_REV – FPGA Revision Number</b><br>FPGA design revision number, lower 4 bits define minor revision change and upper 4 bots define major revision change |

| 7:0  | RO<br>h             | <b>PCB_REV – PCB Revision Number</b><br>PCB design revision number, lower 4 bits define minor revision change and upper 4 bits define major revision change    |

#### 5.3. FCCRS – Function Card Control and Status Register

This is control and status register of the function card.

| Bit   | Access &<br>Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | R/W<br>0            | MASTER – Master<br>When the card is a Master, it generates all control signals, needed for the Data<br>Acquisition, internally. If the boards work in standalone configuration then all boards<br>have to be set to Master. If the boards are configured for the synchronous sampling<br>then only one board can be switched to be Master.<br>0 : the board is a Slave<br>1 : the board is a Master                                                                                                                                                                                                                                                                                                                                                     |

|       |                     | <ul> <li>USAGE</li> <li>Can be changed only in IDLE_ST</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 14    |                     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13    | RO<br>h             | <ul> <li>DA_END - Data Acquisition End</li> <li>The bit is set by hardware after the normal end of Data Acquisition or when the DA_SKIP has been performed. It is not set if Data Acquisition ends with the error.</li> <li>This bit is cleared on arming command or clearing command. <ol> <li>DA ended</li> </ol> </li> <li>USAGE <ul> <li>This bit can be used to detect the end of the Data Acquisition. There are possible two ways: polling the bit or waiting for interrupt generated by this bit when either Output Trigger or Direct Interrupt was enabled. The Data Acquisition stop condition depends on the card configuration.</li> <li>This bit is not set if Data Acquisition is ended by error or software reset</li> </ul> </li> </ul> |

| 12:10 | RO<br>h             | MAINSM_ST – Main State Machine States<br>The bits indicate the states of the main state machine.<br>000 : IDLE_ST<br>001 : DDSUD_ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |